作者简介:田宝凤(1978-),女,副教授,博士.研究方向:核磁共振地下水探测方法和弱信号检测技术.E-mail:tianbf@jlu.edu.cn

设计并实现了基于混合信号处理器(Mixed signal processor 430, MSP 430)和现场可编程门阵列(Field programmable gate array, FPGA)双控制器的拉莫尔频率范围内(1~3 kHz)的电磁噪声测试系统。该系统采用并联低噪声运放减小等效输入噪声,通过程控窄带滤波控制通带带宽和128级增益可调,实现了对复杂空间环境下电磁噪声信息的获取;FPGA内建NIOSⅡ软核搭建数据采集系统,基于SPI总线实现数据在SD卡中的高效、快速存储。通过对室内、外实测数据的分析,验证了该系统设计的有效性。

An electromagnetic noise test system based on MSP430 and Field Programmable Gate Array (FPGA) dual controller in the larmor frequency range 1 kHz ~ 3 kHz is designed. The system reduces equivalent input noise by the parallel low noise operational amplifiers. The system realizes the controllable passband and adjustable 128 gain level to get more information about the current environment of electromagnetic noise. NIOS II soft core built in FPGA is used to set up data acquisition system, and the data are archived in the SD card by the SPI bus so as to realize effective data acquisition and storage. Analysis of the indoor and outdoor measured data verifies the effectiveness of the system.

磁共振测深是目前国际上唯一一种直接探测地下水的地球物理方法[1], 其探测结果通过反演解释可以给出含水量大小、位置以及含水介质孔隙度等定量信息, 因而该方法被广泛应用于缺水地区的地下水资源勘查、评价以及由地下水引起的堤坝渗漏、滑坡、海水入侵等地质灾害水源的探测预警中[2, 3]。然而, 磁共振探水仪在应用的过程中极易受到环境电磁噪声的干扰, 导致接收信号质量较差, 影响数据反演解释结果的可信度[4, 5, 6, 7]。因此, 在仪器工作前, 对拉莫尔频率范围附近的环境噪声进行测试显得尤为重要, 这将决定仪器工作阈值、放大器Q值等参数的设置以及仪器工作方式、线圈铺设方式的选择。

目前, 拥有地面核磁共振(SNMR)探测地下水技术的国家有俄罗斯、法国、中国和美国, 产品化的仪器设备包括法国IRIS公司生产的NUMIS系统、NUMISplus系统、NUMISpoly系统、美国Vista Clara公司的GeoMRI系统以及中国JLMRS-I型找水仪, 这些仪器均各有特色地采用不同的方式实现了对地下水资源的有效探测[8, 9, 10, 11]。法国IRIS公司曾推出与找水仪配套的环境电磁噪声分析仪, 但该噪声分析仪只能大致估测野外环境噪声的大小, 无法给出具体的噪声类型以指导仪器工作方案和相关参数的确定[12]。中国吉林大学JLMRS-I型找水仪科研团队曾研制基于单片机89C54的噪声检测仪器实现对环境噪声的采集, 但仪器的采样速率为10 kHz, 采样速率偏低, 从而导致频率分辨率下降, 影响对噪声成分的精确完整性分析[13]。因而, 仅采用单一的MSP430单片机不能够满足数据的快速采集和大数据量的存储。

鉴于现场可编程门阵列(Field programmable gace array, FPGA)具有可以通过内建NIOS II来实现数据快速采集的优势, 本文提出基于MSP430和FPGA双控制器开展电磁噪声测试系统的设计。信号调理部分通过对运放等效输入噪声的理论计算, 提出采用多级并联方式实现前置低噪声放大电路的设计。提出程控窄带滤波电路与级间RC选频衰减网络相结合的方式, 在避免放大输出饱和的同时, 能够实现良好的频带控制。通过采用程控放大器实现多种增益的选择, 扩大了系统的测量范围。数字主控部分采用双控制器, 利用MSP430搭建非实时的用户接口, 根据用户设置控制各级程控单元。采用FPGA内建NIOSⅡ 软核的方式, 实现了高速数据采集和存储, 并通过SPI总线将数据转存于SD卡。最后, 通过室内外的环境噪声测量, 验证了系统的有效性。

目前磁共振测深常见的环境电磁噪声主要有工频谐波噪声、平稳环境噪声和奇异噪声3种。工频谐波噪声是指由电力线50 Hz或者60 Hz所产生的谐波干扰, 即窄带噪声; 平稳环境噪声是指频谱平坦的纯随机噪声, 即白噪声和带限白噪声; 奇异噪声是由噪声源偶然产生, 且没有固定频率和规律的尖峰噪声, 即脉冲噪声。

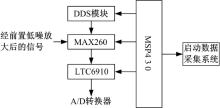

由于噪声类型复杂, 数据量大, 若要实现高速实时的数据采集, 单一的控制器已经无法满足系统的要求, 因此使用MSP430和FPGA双控制器实现整个系统的构建。MSP430F149单片机作为主控制器, 实现对各级程控单元的控制以及实时的用户接口设计; FPGA具有高速特性, 实现数据的采集和存储。系统设计结构框图如图1所示。

由图1可知, 该环境噪声测试系统通过接收线圈获取环境电磁噪声, 接收到的信号经前置低噪声放大电路进行放大, 在MSP430单片机的控制下, 经程控窄带滤波器进行选频, 末级程控放大器将信号进行程控放大, 放大后的信号经模数转换电路全波采样实现模拟量到数字量的转换。FPGA通过SOPC BUILDER内建NIOS软核, 配合Verilog HDL编写的时序逻辑完成数据的采集和存储, 最后通过SPI总线将采集的数据存储于SD卡。

线圈接收环境电磁噪声信号, 与配谐电容组成一个LC谐振回路。由于不同地区的地磁场强度不同, 导致不同地区的氢质子的拉莫尔频率也不相同, 谐振频点依据当地氢质子的拉莫尔频率(1~3 kHz)设定。考虑到测量者携带的便利性, 线圈使用粗导线缠制50匝30 cm× 30 cm的方形线圈构成, 测得线圈的电感L=0.75 mH, 将LC电路的谐振频率取为当地的拉莫尔频率, 配谐电容由式(1)计算:

当拉莫尔频率f=2326 Hz时, 所需的配谐电容C=6.24× 10-6F。设计电路采用3个2 μ F电容并联成6 μ F的精密电容, 利用Multisim仿真软件可以绘出该电路的波特图, 获得通带增益。根据f=2326 Hz处的增益为14.9 dB, 电压增益可由公式(2)计算得到, 计算出的电压增益为NLC=VOUT/VIN=5.56。

式中:VOUT、VIN分别为LC谐振回路的输出、输入电压。

2.2.1 电路设计的理论计算

电路内部的噪声源使电路在无激励时仍然存在输出。为此使用等效输入噪声电压来衡量电路的噪声水平, 即把从电路输出端测得的噪声电压有效值Von折算到该电路的输入端, 方法是除以该电路的增益K, 得到的数值称为该电路的等效输入噪声电压Vin:

若电路输入端的信号Vts的幅值比后级电路的等效输入噪声电压Vin还要低, 则该信号就会淹没在电路的本底噪声中, 从而导致在后级电路中无法区分该有用信号和电路的本底噪声。由于前后级在噪声方面是互不相干的随机噪声, 故:

式中:Vino为前置放大器本身的输入噪声电压; Vin为后级电路的输入噪声电压; Von为后级电路的输出噪声电压; Ko为前级放大电路增益。

总的等效输入噪声电压(按电压增益折算回输入端)为:

当输入信号Vis与后级电路输入噪声电压Vin相等时, 即Vis=Vin, 此时输入信号刚好淹没于电路的本底噪声中。为了能够从电路的本底噪声中区分出输入信号Vis, 有关系式Vis> V'in。根据Vis=Vin, 则需要Vin> V'in, 即:

得到:

由式(7)可知, 该前放本身的等效输入噪声电压Vino必须低于后级电路的等效输入噪声电压Vin, 才能使有用信号在电路中与噪声区分开来, 这也是在电路前端必须加入前置低噪声放大电路的原因。

2.2.2 并联低噪声放大电路的构建

由于通过线圈耦合进来的电磁噪声是纳伏级的小信号, LT1028采用非对称输入方式, 在1~3 kHz范围内有很好的特性, 因而设计中选用该芯片来实现前置放大电路的构造。依其噪声特性可知, 在1 kHz时, 电压噪声密度Sn为0.85 nV/

得到:

由此可知, 由电流引起的前端输出信号的电压噪声密度远远低于其固有的电压噪声密度, 因而在该系统设计中电压噪声密度占主要作用。

为了避免串联方式运算放大器等效输入噪声电压过高的缺点, 设计中采用并联方式通过对信号的多次叠加来提高信噪比。根据芯片资料可知, 单级LT1028与7.5 Ω 的源电阻共同产生的电压噪声密度为0.9 nV/

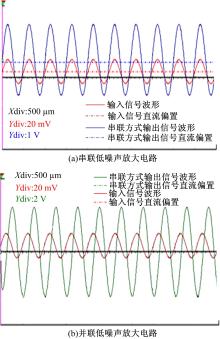

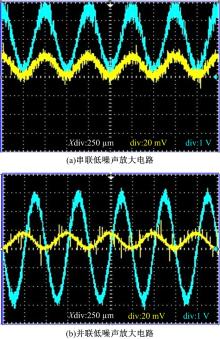

两级放大中间采用一个0.1 μ F的电容实现电容耦合, 从而对前级电路的直流偏置起到一定的抑制作用。图2为两种方式运算放大器的仿真效果对比图, 图3为两种方式运算放大器的实测效果图(黄色线为输入, 蓝色线为输出)。对比图2和图3, 实测数据进一步验证了仿真结果的正确性, 同时可以看出串联方式的直流偏置没有得到抑制, 而并联方式的直流偏置接近于零, 从而避免后级放大时出现饱和现象。

2.3.1 程控窄带滤波电路的设计

在磁共振测深的过程中, 测点不同, 响应信号的频率在1~3 kHz之间变化, 所以要求窄带滤波器的中心频率可调节; 不同环境下, 噪声的幅值不同, 所以要求滤波器通带增益可调。MAX260是一款CMOS双二阶通用开关电容滤波器, 可实现各种低通、高通、带通、全通以及陷波的配置。因而, 设计中采用两片MAX260构成4级带通滤波器, 均工作于方式一, 方式一具有最大带宽, 这样所能考察的通带会更宽, 以获得更多关于当前环境下电磁噪声的信息。工作方式与滤波器功能的关系如表1所示。

| 表1 工作方式与滤波器功能的关系 Table 1 Relationsip between works and filter function |

通带增益满足:Q=

中心频率满足:

式中:NQ和NF分别表示对应品质因数和中心频率的控制字; fclk为输入时钟频率。

由于通过改变fclk来改变中心频率fo, 所以需要fclk可调节, 并达到一定的精度, 因此使用高精度的直接式数字频率合成器(Direct digital synthesizer, DDS)来实现。

2.3.2 级间RC选频衰减网络

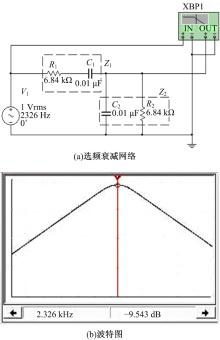

为了提高电路的滤波效果, Q值会设置得较高, 这会导致在MAX260输出端出现饱和现象。为避免这一现象以及提高电路的选频能力, 在MAX260级间增加RC选频衰减网络。图4给出了在Multisim中搭建的RC选频衰减网络以及波特图。

下面给出阻抗匹配选频衰减网络电路特性的理论推导。

令R1=R2=R; C1=C2=C, 则反馈网络的反馈系数为:

就实际频率而言, 令s=jω , 则得:

若令ω o=1/RC, 则公式(16)变为:

由式(17)可以获知该选频衰减网络的幅频响应及相频响应为:

由式(18)(19)可知, 当ω =ω o=1/RC时, 即:

其幅频响应的幅值为最大, 即:FVmax=1/3。而在该频点时的相位角φ f=0。

根据上述推导, 当ω =ω o=1/RC时, 电路处于振荡工作状态, 完成选频功能, 输出电压幅值达到最大值, 同时输出电压是原始输入信号的1/3。选择长春地区氢质子拉莫尔频率f=2326 Hz作为选频的频点, 取电容C=0.01 μ F, 可计算得到R=6.84 kHz。在实际应用中选用四个滤波单元间连接了3个RC选频衰减网络, 电路的通带增益为:

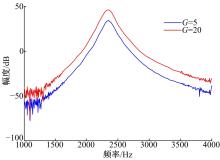

图5为采用上述技术改变Q值时窄带滤波器的实测幅频特性图。中心频率fo设置为2326 Hz, 随着Q值的增加, 频带宽度减小, 增益逐渐变大。

2.3.3 程控放大器

为了将野外微弱的纳伏级环境噪声放大到模数转换器ADS8505的工作范围以内, 要求系统的整体放大倍数达到至少120 dB。根据上述分析, 前置放大器的放大倍数可以达到50 dB, 窄带滤波及阻容网络可以形成20~60 dB的通频带增益, 因而, 后级需要进一步采用程控放大器实现约40 dB的放大才能满足要求。

LTC6910-1程控放大器有输入噪声低、通带增益灵活可调等优点而被采用。图6给出了中心频率固定, 程控窄带滤波器的参数保持不变, 只改变程控放大器放大倍数的测试结果。图中蓝线中心频率处的放大倍数是34.26 dB, 红线为46.43 dB, 红线显示放大倍数是蓝线的4.0598倍, 这与实际设置的放大倍数是一致的。

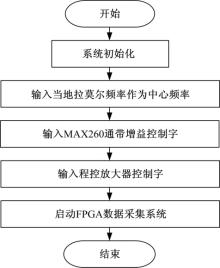

MSP430单片机具有超低功耗、低电压供电、工作消耗电流极小等特点, 因而被用作系统的主控制器。主控电路主要由MSP430、DDS模块、MAX260滤波器和LTC6910程控放大器构成。图7为控制系统的结构框图。

图7中, DDS模块由AD9850实现, 片内含有可编程的DDS系统和高速比较器, 可实现全数字编程控制的频率合成, 得到的频率即MAX260的时钟频率fclk。经前置低噪放大器放大后的信号通过MAX260实现窄带滤波, 获取1~3 kHz的有用信号。然后, 程控放大器LTC6910将滤波后的微弱信号放大到A/D转换器的工作范围内, 以确保数据的量化。其中, AD9850、MAX260以及LTC6910的逻辑控制字均由MSP430写入。MSP430在实现对各个程控单元的控制后, 启动基于FPGA的数据采集系统。相应的控制系统程序设计流程如图8所示。

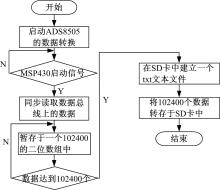

野外环境噪声通过信号接收及调理电路被放大到足够的范围, 为了能够对其进行进一步的分析和处理, 获取更全面的信息, 就需要对该模拟信号进行采集和存储。采集系统由ALTERA公司的EP2C8Q208C8N构建, 利用FPGA内建NIOSII搭建数据采集系统的控制逻辑。主要包括两部分:一是通过Verilog HDL编写的分频程序; 二是NIOSⅡ 构建的数据采集和存储电路。数据采集系统框图如图9所示。

FPGA的外部时钟由50 MHz的晶振提供, 对该时钟进行分频后得到ADS8505的工作时钟, 实现占空比为14/18的周期数字信号并作用于ADS8505。NIOSⅡ 软核内置的锁相环(Phase locked loop, PLL)的工作时钟与SDRAM具有-75° 的相位差, 以确保系统的正常运行。NIOSⅡ 工作在100 MHz, 采用中断的方式, 根据转换时钟同步读取Avalon总线上的数据, 暂存后由SPI总线转存于SD卡。

图10为FPGA内建SOPC的程序流程图, FPGA作为数据采集系统的主控制器, 采用中断的模式控制R/C时序, 在每个R/C上升沿实现数据的读取, 同步启动ADS8505进行模数转换。

为了验证测试系统的效果, 分别在实验室和野外进行了测试实验, 运用MATLAB数据处理软件对SD卡中存储的数据进行了读取和频谱分析。

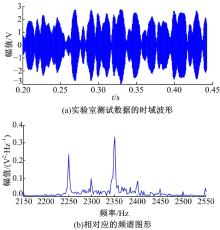

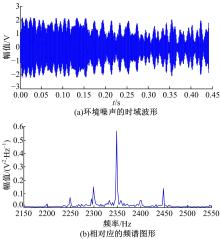

图11(a)是在前置放大器放大倍数为316倍、窄带滤波器的通带增益为Q=479倍、通带中心频点为2326 Hz、程控放大器增益为1时采集的实验室内环境噪声的时域波形。该组数据的频谱如图11(b)所示。在同样的测试条件下, 图12给出了近似无噪声情况下的本底噪声测试分析。

对比图11和图12的时域波形可以看出:系统本底噪声的幅值在0 V左右, 而环境噪声的幅值为-3~+3 V; 从频谱图亦可以看出环境噪声比本底噪声有着较为明显的幅频特性。

由图11(a)和(b)可以看出, 实验室内空间狭窄, 环境噪声干扰源较多, 干扰较为严重, 存在2250、2300、2350、2400、2450、2500 Hz等间隔为50 Hz的谐波干扰, 此外还包括一些其他频率成分的噪声。为了进行对比分析, 图13给出了采用泰克公司的DS1102C型双踪数字示波器获得的信号局部波形以及分析的频谱图。

由图13可以看出:示波器也分析出了2350 Hz处主要谐波干扰频率成分, 但其FFT实时变换功能, 由于加窗和数据截断导致频谱分析不能获得本测试系统所能达到的分析精度。

关于野外环境噪声测试了两组数据, 测试条件为:系统工作在通带中心频率为2326 Hz、窄带滤波器的通带增益为NQ=122, 即Q=479、程控增益为1的状态。第一组数据是在长春市文化广场地质宫外科技之星附近测得, 图14(a)(b)分别给出了环境噪声的时频域波形。

由图14(a)(b)可以看出:该测试地点相对于实验室, 不存在有限空间环境下复杂的噪声源。由实测情况也可以看出:干扰的主要成分为工频谐波的整数倍, 尤其频率为2350 Hz处的干扰影响最大, 含有较小的随机噪声, 不含有尖峰干扰。

第二组数据是在长春市文化广场地质宫楼侧面测得, 图15(a)(b)分别给出了环境噪声的时频域波形。

由图15(a)中的时域波形可以看出, 含有较多的尖峰干扰, 对应图15(b)的频谱图形也可以看出, 在频率为2300~2350 Hz附近有明显的尖峰噪声频谱特性, 同时在频率为2250、2400、2450 Hz附近含有部分工频谐波干扰, 此外也含有较小的随机噪声。

基于MSP430和FPGA双控制器技术, 设计并实现了野外环境噪声测试系统。采用低噪声前放, 通过多级并联降噪的方式实现了微弱纳伏级信号的放大; 程控窄带滤波电路以及级间RC选频衰减网络的采用, 实现了中心频率1~3 kHz可调, 良好的频带控制, 选频效果明显; 末级程控放大电路与通带增益相配合, 实现多种增益的选择, 扩大了系统的测量范围, 放大倍数可达120 dB以上; 实现了基于NIOSⅡ 的高速数据采集系统, 利用SPI总线将数据存储于SD卡中; 采用Matlab数据处理软件实现噪声数据的分析和处理, 能够给出干扰类型和数值大小。

The authors have declared that no competing interests exist.

| [1] |

|

| [2] |

|

| [3] |

|

| [4] |

|

| [5] |

|

| [6] |

|

| [7] |

|

| [8] |

|

| [9] |

|

| [10] |

|

| [11] |

|

| [12] |

|

| [13] |

|