作者简介:王春悦(1971-),女,副教授,博士.研究方向:信号与信息处理.E-mail:chunyue@jlu.edu.cn

由于无源电感不易集成,本文提出了一种新的基于改进的差动差分电流传送器 (MDDCC)的理想浮地电感,分析了电流传输器在理想情况和非理想情况下的电感值,该电路仅由2个MDDCC,2个电阻和1个电容构成,结构简单,电感值可由阻容元件独立调节.将此电路用于电压模式二阶低通和二阶带通以及电流模式高阶的连续时间滤波器中,用参数为0.18 μm CMOS工艺进行PSPICE计算机仿真.仿真结果表明,设计方案是可行有效的.

Because that the passive inductance is not easy to be integrated, a new ideal floating inductance based on Modify Differential Difference Current Conveyor (MDDCC) is proposed. The inductance values of the current conveyor in ideal and nonideal conditions are analyzed. This circuit consists of only two MDDCCs, two resistors and one grounded capacitor. So the structure of the floating inductance is simple, the inductance value can be adjusted independently by the two resistors and the capacitor. The circuit is used in continuous time voltage mode filter of two order low pass, and two order band pass and current mode high order filters. Computer simulation of PSPICE is carried out using parameters of the 0.18 μm CMOS process. Simulation results show that the proposed floating inductance has good circuit's work ability.

滤波器实现技术按处理信号的类型分为采样数据技术(采样滤波器)和连续时间技术(模拟滤波器), 开关电容(SC)是典型的采样数据滤波器.采样数据滤波器的共同缺点是系统工作频率受奈奎斯特采样定理的限制; 因采样带来的时钟馈入问题导致滤波器精度下降, 噪声和失真增加.另外, 采样数据滤波器对连续时间信号进行滤波时, 需在前端加防混叠滤波器对输入信号作带限处理, 在后端加平滑滤波器以满足采样定理并得到平滑的输出.所以, 能够克服上述缺点的最佳方案就是对连续时间信号直接滤波, 即全集成连续时间滤波器.近年来, 全集成连续时间滤波器的发展特别迅速, 在通信集成电路如无线传感器网络[1], 模数转换[2, 3], 无线接收机[4, 5]等技术中得到了成功的应用.电流传输器是一种功能很强的混合模式通用滤波器件[6, 7, 8, 9, 10, 11], 它广泛应用于模拟信号处理和有源网络元件的模拟电路中[12, 13, 14, 15, 16, 17].改进的差动差分电流传输器(Modify differential difference current conveyor, MDDCC)集合了电流传输器和差动差分放大器的优点[6], 易于集成.在模拟滤波器设计中由于无源器件体积大, 耗电量大, 不利于集成, 所以提出了用改进的电流传输器来实现模拟电感, 模拟电感滤波器具有结构设计简单, 无源元件的灵敏度低的特点, 是一种有效的全集成连续时间高级滤波器设计方法.

本文分析了模拟电感在理想特性情况下和非理想特性情况下的电感值, 并将其应用到电压模式二阶低通和二阶带通滤波器和电流模式三阶巴特沃斯和五阶切比雪夫低通滤波器中.仿真结果表明, 提出的滤波器电路是可行的, 所构成的滤波器性能符合设计指标的要求.

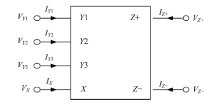

MDDCC是一个具有四端输入双端输出的六端口有源器件, 端口伏安特性如式(1)所示:

由MDDCC的端口伏安特性可以看出,

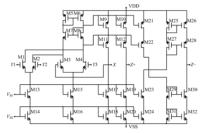

图2给出了MDDCC的CMOS电路, 输入级由M1~M8, M13~M16组成, 差动电压传送由差分对M1, M2及M3, M4完成.M5, M6和M7, M8构成电流镜, 静态时M1和M4的漏电流之和等于M2和M3的漏电流之和, 即Id1+Id4=Id2+Id3, 因此Id1-Id2=Id3-Id4, VG1-VG2=VG3-VG4, 其中VG1=VY1, VG2=VY2, VG3=VX, VG4=VY3, 从而得到

| 图2 MDDCC的CMOS电路[11]Fig.2 CMOS Circuit of MDDCC |

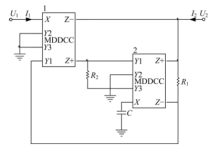

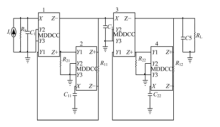

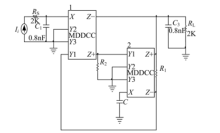

图3为本文提出的新的浮地电感模拟电路, 该电路由2个MDDCC, 2个电阻和1个电容组成, 电路结构简单.

对图3的端口特性进行分析, 有:

式(6)写成矩阵形式为:

对图3电路分析其端口的短路导纳矩阵为:

由式(8)可知电路的等效电感为:

此电路有以下两个特点:所需要的元器件很少, 只用2个MDDCC和1个电容, 2个电阻; 元件间无约束, 电感值可以任意调节.如若考虑非理想特性的影响, 只考虑电压对特性的影响, 则MDDCC的输入输出特性可表示为:

则电路的导纳为:

其理想浮地等效电感为:

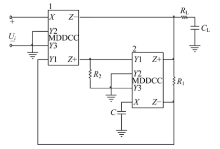

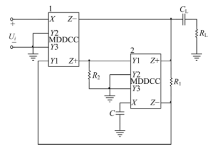

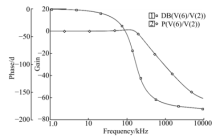

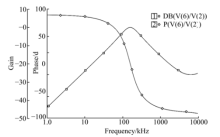

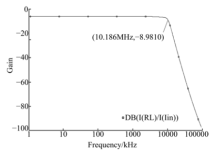

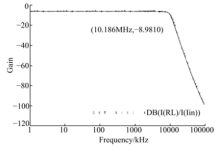

把本文提出的理想浮地电感实现电路应用于电压模式二阶低通滤波器(见图4)和二阶带通滤波器(见图5)的设计当中, 并用PSPICE仿真.设计频率

仿真时, 令L=10mH, R1=R2=10kΩ , C=0.1nF, 计算出RL=10kΩ , CL=0.1nF, 从而得出图4, 图5的仿真图, 见图6, 图7.从仿真结果可以看出, 低通滤波器的实际截止频率为

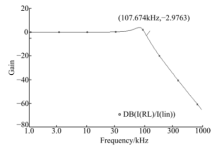

本文提出的浮地电感不仅可以应用于传统的电压模式连续时间滤波器中, 还可以应用于新型的电流模式连续时间滤波器中, 用提出的模拟浮地电感应用于三阶巴特沃斯LC无源梯形滤波器电路当中[13], 设计截止频率

| 图8 三阶巴特沃斯低通滤波器[13]Fig.8 Third-order Butterworth low pass filter |

提出了一种新的基于MDDCC的模拟浮地电感, 该电路仅用2个MDDCC, 2个电阻和1个电容, 电路结构简单, 易于集成, 等效电感可由电阻和电容独立调节, 将其用于二阶电压模式低通和带通滤波器以及电流模式三阶巴特沃斯和五阶切比雪夫滤波器的设计, 仿真结果证实了设计电路的正确性, 且具有易于集成, 结构简单, 无源元件少, 灵敏度低等优点.

The authors have declared that no competing interests exist.

| [1] |

|

| [2] |

|

| [3] |

|

| [4] |

|

| [5] |

|

| [6] |

|

| [7] |

|

| [8] |

|

| [9] |

|

| [10] |

|

| [11] |

|

| [12] |

|

| [13] |

|

| [14] |

|

| [15] |

|

| [16] |

|

| [17] |

|