作者简介:隋延林(1992-),男,博士研究生.研究方向:信号与图像处理.E-mail:suiyanlin1992@163.com

基于现场可编程门阵列(FPGA) XC6LX100T设计了两套CameraLink接口传输的硬件平台,提出在实验中结合使用片上调试工具Chipscope和同步发生源模块用于精确测量FPGA中的传输误码的方法,详细对比了基于FPGA设计的CameraLink接口与DS90CR287、DS90CR288A的传输效果。结果表明:相对现今主流CameraLink接口电路,本文使用低压差分对代替大量并行数据线,最高可支持154 MHz像素时钟,单个CameraLink接口的传输速率可达4.31 Gbit/s,突破了串并转换芯片传输速率的瓶颈, FPGA直接输出的CameraLink数据可以驱动6 m的CameraLink传输线,图像可长时间正常无误显示,设计的系统可应用于各种基于CameraLink接口的传输系统。

Based on Field Programmable Gate Array (FPGA), two sets of CameraLink interface transfer hardware platform are designed to compare serial-parallel converter chip and CameraLink interface based on FPGA). A new method, in which on-chip debugging tool Chipscope is combined with synchronized generation module, is proposed to detect error data accurately. The results show that CameraLink interface based on FPGA uses fewer pins with higher speed transmission rates. Single port supports a maximum transfer rate of 4.31 Gbit/s when the pixel clock is 154 MHz. The CameraLink data output can drive 6 m CameraLink transmission line, with no bit error appears for long hours, and it can be used in a variety of different systems based on CameraLink interface.

目前, 基于CameraLink接口的数据发送和接收, 大多采用专用的串并转换芯片DS90CR287、DS90CR288A与相机进行数据传输[1, 2, 3, 4, 5], 美国国家太阳观测站的AO76系统需要相机在200× 200 像素下达到2487 帧/s[6], 文献[7]提到的ESO AOWFS和AONGC需要帧频1500 帧/s。一直以来各种光学系统对相机的高速传输有强烈的需求。使用串并转换芯片不仅会使得并行信号占用大量布局布线资源, 占用体积面积, 而且在现今FPGA的功能日益完善、数据量日益膨胀的背景下, CameraLink串并芯片最高传输速率有限, 已然成为CameraLink数据传输系统的单个接口速率瓶颈。如今的FPGA已内部集成串并转换模块, 可以替代专用的串并转换芯片, 并且速率更快。在实际应用中, CameraLink接口硬件系统的高集成度、小体积和高速率的特性可以用于无人机, 也可应用于民用医疗、视频显示等。文献[8]针对用于LCD显示的并转串驱动器芯片SN75LVDS83B设计了基于FPGA的CameraLink接口, 但是SN75LVDS83B实际上是Flatlink接口芯片, 而且并没有串转并的接口设计, 没有提及实现的最高速率和误码率测试, 无对比实验, 不能体现基于FPGA的CameraLink接口的通用性、优越性和先进性。

为了实现基于CameraLink接口的数据传输低成本、小体积、高速率、更稳定的传输, 就要设计一套硬件系统平台, 在不通过CameraLink芯片的情况下完成更高速率、无误码的传输并显示。基于此, 本文以基于FPGA的CameraLink接口和主流串并转换芯片DS90CR287、DS90CR288A为研究对象, 设计了两套硬件系统, 对比最高速率、信号波形、传输误码、驱动能力, 通过实验反映基于FPGA的CameraLink接口的先进性。

CameraLink图像数据在串行传输时采用的是低压差分信号技术(LVDS), 使用非常低幅度信号(大约350 mV), 通过一对差分PCB走线或平衡电缆传输数据。

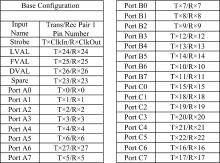

CameraLink硬件结构分为三类:基础结构(Base)、中间结构(Medium)和完全结构(Full)。根据CameraLink的硬件结构分析, 在系统输入端选用一个MDR26或SDR26连接器构建CameraLink的Base结构即可用来接收相机输出的串行数据信号。

CameraLink信号分为图像数据信号、相机控制信号、异步串行通信信号和电源信号。本文以BASE模式为例研究, 如图1所示, 其中数据信号28位, 由1位帧有效信号、1位行有效信号、24位数据有效信号和保留信号组成。目前, 实际工程中大多采用专用的串并转换芯片DS90CR287、DS90CR288A实现28位的图像数据信号和1位的时钟信号与5对LVDS的低压差分信号的转换, 实现DS90CR287图像信号的传输。这两款芯片的时钟频率最高为85 MHz, 最高的传输数据率为2.38 Gbit/s, 有效数据率为2.04 Gbit/s。

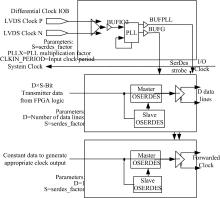

并串转换模块的作用与CameraLink图像专用并转串芯片DS90CR287相同, 28位图像数据分成4组, 每组进行7∶ 1的并串转换, 由于Spraten6系列I/O上的OSERDES最高只支持4∶ 1的转换, 所以将两个OSERDES串联起来, 分成主从模块, 如图2所示, 得到7∶ 1的转换。同样, 像素时钟需要按照CameraLink时钟格式1111000进行7∶ 1的并串转换, 最终得到4组LVDS图像信号与一组LVDS时钟信号连接至CameraLink接口输出, 可以实现在FPGA上对CameraLink图像的并串转换, 通过FPGA直接发送LVDS图像数据, 以及最高像素时钟为154 MHz的并串CameraLink图像转换。Xilinx公司的Spartan6系列XC6LX100T-3FGG676内部锁相环PLL, 用于生成各模块使用的时钟信号, BUFPLL根据PLL的时钟和串并转化的比例, 生成高速串行时钟IOCLK供ISERDES和OSERDES原语使用[9], 根据文献[10]和实验调试结果证明, PLL的最高输出频率为1080 MHz, 所以提供给BUFPLL的高速时钟IOCLK为1080 MHz, CameraLink图像串并转换需要1∶ 7, 故内部的并行慢时钟最高为154.3 MHz, 本文选择验证最高能实现的像素时钟为154 MHz。

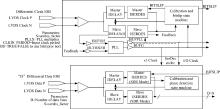

相对于并串转换模块, 基于FPGA开发的串并转换模块难点在于输入的信号需要进行适当延迟, 保证数据能被ISERDES模块正确采样。如图3所示[12], 使用IODELAY原语和相位检测模块, 其中相位检测模块由状态机构成, 使采样时从模块输入延迟能有效控制主输入延迟, 避免数据丢失。其作用与CameraLink图像专用串转并芯片DS90CR288A相同, 4组LVDS图像信号与1组LVDS时钟信号, 通过Spartan6系列的I/O模块上的两个串联的ISERDES进行1∶ 7的转换, 最终得到28位并行图像数据与像素时钟信号。可以在FPGA上实现对CameraLink图像的串并转换并且直接通过FPGA以LVDS接收图像数据, 同样最高能实现像素时钟为154 MHz的串并CameraLink图像转换。

本文基于FPGA设计的串转并模块和并转串模块, 针对CameraLink图像格式可实现154 MHz的最高工作频率, 传输数据率可达4.31 Gbit/s(有效数据率3.70 Gbit/s), 突破了转换芯片的速率瓶颈, 5路LVDS直接与FPGA互连, 大大节省了布局布线和电路体积, 节约了成本。

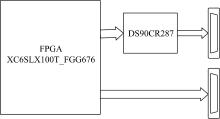

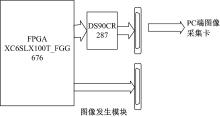

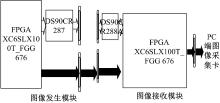

本文设计的硬件平台由包括基于Xilinx公司的Spartan6系列FPGA XC6LX100T-3FGG676的图像发生模块和同样基于FPGA XC6LX100T-3FGG676的数据传送模块组成。图像发生模块通过预设的程序自发生成两路完全相同28位CameraLink图像数据和1位像素时钟信号用于发送, 一路通过CameraLink图像专用并转串芯片DS90CR287发送, 另一路直接通过本文基于FPGA开发的CameraLink并串转换模块, LVDS直接输出。数据传送模块有两路接收CameraLink图像数据, 一路通过CameraLink图像专用串转并芯片DS90CR288A芯片接收, 另一路由本文基于FPGA开发的CameraLink串并转换模块, 并由FPGA直接接收。输出端通过本文基于FPGA开发的CameraLink并串转换模块, LVDS直接输出。

如图4所示, 根据CameraLink图像数据格式, 图像发生模块预设的程序自发生成两路完全相同的28位CameraLink图像数据和1位像素时钟信号用于发送BASE模式的图像。

图像发生板上的基于FPGA开发的图像自发生模块由图像自发生模块和并串转换模块组成。图像自发生模块的作用是FPGA自发产生像素时钟可调的10 bit格式图像, 并在图像数据中加入专用同步码, 为后文实验准确测量传输误码使用, 如图5所示, 左侧为等间距黑白条纹, 右侧有斜条纹, 上下有距离依次增大的5个灰度段, 作为图像发生源, 可以通过观察图像来判断横向、纵向上是否失真。

本实验一路通过CameraLink图像专用并转串芯片DS90CR287发送80 MHz像素时钟的图像; 另一路直接通过本文基于FPGA开发的CameraLink并串转换模块, LVDS直接输出像素时钟依次为80、90、154 MHz的图像。通过Modelsim仿真80 MHz像素时钟的图像得到的时序图如图6所示。

如图7所示, 数据传送模块分两路接收图像数据, 一路通过CameraLink图像专用串转并芯片DS90CR288A接收像素时钟依次为80、90 MHz的图像, 另一路通过本文基于FPGA开发的CameraLink串并转换模块接收像素时钟依次为80、90、154 MHz的图像, 输出端由FPGA直接发送其中像素时钟为90、154 MHz的图像, 在FPGA内经过二分频处理再发送。

提出了一种同步自发生模块与Chipscope检测功能相结合的方法, 能准确测量本文设计的串并转换模块的数据传输误码。

片上调试工具Chipscope检测功能是Xilinx的ISE开发套件中自带的软件工具, 可以实时、准确地观察FPGA片内的各信号波形, 在本次实验中用于检验对比FPGA接收到的图像数据与同步自发产生的图像数据, 如果出现不同会报错计数。在本文设计的同步图像数据发生模块ISE内添加一个模块, 作用是根据接收到的图像数据信号中的专用同步码, 产生与原始图像完全相同的图像数据, 并且在信号序列上实现同步, 再与接收到的图像数据信号进行对比, 如果信号不一致, 会产生报错计数, 使用Chipscope检测工具观察FPGA内部接收到的信号和报错信号。

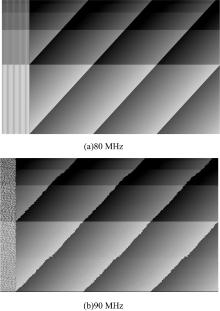

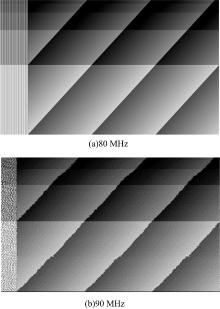

实验示意图如图8所示。因为目前绝大多数PC端的图像采集卡最高只能接收85 MHz像素时钟的CameraLink图像, 本文实验所使用的图像采集卡是Matrox的Solios, 采集卡上使用DS90CR288A接收图像, 最高能采集85 MHz像素时钟的图像, 所以先设计图像的像素时钟为80、90MHz, 通过DS90CR287芯片发送的信号经SDR26接口通过CameraLink传输线连接到PC端的图像采集卡, 观察的图像如图9所示。本文实验所用的CameraLink传输线长均为6 m。

Matrox的Solios采集卡采集到的80 MHz像素时钟的原始图像无失真, 图像正确, 90 MHz像素时钟的图像因为通过DS90CR287发送数据并且采集卡上用DS90CR288A, 导致图像失真。实验现象为后文作对比。

如图8所示, 图像发生模块的条纹图像另一路通过本文设计的基于FPGA的LVDS输出模块经SDR26接口连接到同一个PC端的采集卡, 分别输出像素时钟为80、90 MHz的相同图像, 如图10所示。

| 图10 FPGA并串转换模块输出80、90MHz图像Fig.10 FPGA output 80 and 90 MHz image with parallel-serial converter module |

观察可发现, 两种输出方式得到的图像结果没有差异, 本文基于FPGA设计的LVDS发送图像与通过CameraLink图像专用并转串芯片DS90CR287发送的图像在80 MHz下作用相同, 90 MHz下通过Matrox的Solios采集卡采集到的图像都出现了失真。

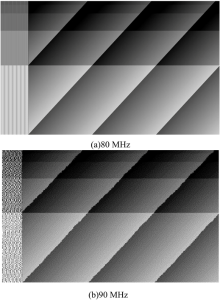

如图11所示, 图像发生模块的条纹图像另一路通过本文设计的基于FPGA的LVDS输出模块经SDR接口连接至图像传输模块的DS90CR288A芯片, 图像传输模块的输出端通过本文设计的基于FPGA的LVDS输出模块经SDR26接口连接到PC端的采集卡, 分别输出像素时钟为80、90 MHz的相同图像, 如图12所示。再将90 MHz图像在传输板上的FPGA上进行二分频处理, 排除因图像采集卡上DS90CR288A而无法进行正常接收图像的因素, 观察到的图像如图13所示。

| 图12 经DS90CR288A传输板输出80、90 MHz图像Fig.12 Image transmission board output 80 and 90 MHz image with DS90CR288A |

| 图13 经DS90CR288A传输板并二分频输出90 MHz图像Fig.13 Image transmission board output 90 MHz image with DS90CR288A after two sub-sampling |

在80 MHz下经FPGA直接输出的CameraLink图像经过DS90CR288A接收, 图像没有任何失真。因为传输板和采集卡使用DS90CR288A, 芯片的限制导致图像在90 MHz下因超出工作频率而出现失真。

图14为本文设计的图像通过Modelsim仿真得到的部分波形, 图15为通过调试工具Chipscope得到80 MHz图像实验中, 在传输板上截取FPGA内部相应波形。对比可以发现, 片上调试工具Chipscope可以实时、准确地观察FPGA片内的各信号波形。

本文的传输模块板的FPGA中设计有同步图像数据发生模块和Chipscope检测功能, 同步图像数据发生模块会产生与原始图像完全相同的图像数据, 并且在信号序列上实现同步, 再与接收到的图像数据信号进行对比, 如果信号不一致, 会产生报错计数, 使用Chipscope检测工具, 观察FPGA内部接收到的信号和报错信号。

通过DS90CR288A接收到的80 MHz的图像数据与串并转换得到的图像数据完全相同, 并且持续半小时没有报错计数, 说明没有误码, 如图16所示。在90 MHz时, 因为传输板上使用S90CR288A芯片, 无法正确接收90 MHz的图像数据信号, FPGA接收到的图像数据与同步发生的数据不符, Chipscope中一直在计数报错, 如图17所示。90 MHz的图像在S90CR288A接收后因为超出工作频率已经使接收的信号出现错误, 经过二分频处理并不改变错误的产生, 如图18所示。

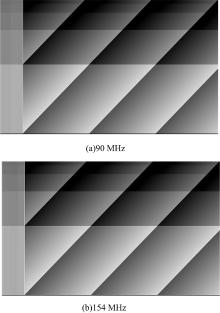

如图19所示, 再将图像发生模块的条纹图像通过本文设计的基于FPGA的LVDS输出模块经SDR接口连接至图像传输模块串并转换模块, 图像传输模块的输出端通过本文设计的基于FPGA的LVDS输出模块经SDR接口连接到PC端的采集卡, 分别输出像素时钟为80、90、154 MHz的相同图像, 先观察80、90 MHz的图像, 如图20所示。

再将90、154 MHz的图像在传输板上的FPGA上进行二分频处理, 因为把图像发生模块的像素时钟提升到154 MHz时无法使用DS90CR287、DS90CR288A和图像采集卡进行正常的发送与接收。观察到的图像如图21所示, 图像比例、条纹间距是原来的一半, 图像没有任何失真。

| 图20 经传输板FPGA接收并输出80、90 MHz图像Fig.20 Image transmission board input and output 80 and 90 MHz image with FPGA |

| 图21 经传输板FPGA接收并二分频输出90、154 MHz图像Fig.21 Image transmission board input and output 90 and 154 MHz image with FPGA after two sub-sampling |

如图22所示, 通过Chipscope检测工具观察传输板FPGA上像素时钟分别为80、90和154 MHz的图像的输出信号可以发现, 图像通过自发生模块直接LVDS输出, LVDS直接接收, 图像数据原始数据完全相同, 持续半小时均没有任何报错。

CameraLink接口模式及带宽与本文方法比较如表1所示。

| 表1 CameraLink接口模式及带宽 Table 1 Modes vs bandwidth of CameraLink interface |

本文设计的硬件平台由基于Xilinx公司Spartan6系列XC6LX100T-3FGG676的图像发生模块和同样基于XC6LX100T-3FGG676的数据传送模块组成。使用ISE14.7开发工具、Modelsim仿真软件、Chipscope波形观察工具、Matrox的图像采集卡在FPGA上和PC端的显示器上进行验证。Modelsim仿真软件观察到的图像发生序列正确, 图像经图像采集卡采集, 在PC端的显示的效果与预期效果一致, 在Chipscope波形观察工具中检测无误码。验证了在FPGA上可以实现对CameraLink图像的并串转换, 通过FPGA可以直接LVDS发送与接收图像数据, 并且最高能实现像素时钟为154 MHz的CameraLink图像并串与串并转换, 大大提升了CameraLink接口的数据传输速率。接收的图像数据可以直接进行处理再输出。

The authors have declared that no competing interests exist.

| [1] |

|

| [2] |

|

| [3] |

|

| [4] |

|

| [5] |

|

| [6] |

|

| [7] |

|

| [8] |

|

| [9] |

|

| [10] |

|

| [11] |

|

| [12] |

|