作者简介:尼启良(1966-),男,研究员,博士.研究方向:软X射线-紫外波段空间应用光子计数成像探测器.E-mail:qiliangni@qq.com

为了提高现有楔条形阳极的光子计数成像探测器的整体计数率,根据探测器输出信号的特点,研制了一个基于高速模数转换(A/D)芯片和现场可编程门阵列(FPGA)的位置读出电路。该电路采用高速A/D芯片(65 MHz采样频率)对整型放大器输出的高斯型脉冲信号逐点数据采样后获取其峰值的方法来代替原有的前端模拟电路中昂贵的峰值保持模块及NI公司的多道数据采集卡,采集的数据通过FPGA进行处理并且通过USB传输到计算机中进行解码,最终还原出图像。试验结果表明:由该电路获得的探测器图像在分辨率基本保持不变的条件下,整体计数率可以提高近一倍。

In order to raise the whole count rate of a wedge-strip anode's photon-counting imaging detector, according to the feature of the signal output from the detector, a position readout circuit was designed and developed. This circuit is based on high speed Analog-Digital (A/D) converters and a Field Programmable Gate Array (FPGA) chip. The circuit employs high speed A/D converters with 65 MHz sapling rate to transform the Gaussian pulse analog signal into digital series at every clock period and obtain the peak value of the pulse signal by a FPGA. It has the functions of peak hold module of voltage pulse and NI data collection card in the original circuit. The FPGS processes the received digital series according to certain rules and sends them to the computer by UBS data interface. The developed software can compute the coordinate position of every photon and display them on PC screen according to obtained 3-way data. The design of the circuit hardware and logic control is described in detail in this paper. Experiment results show that the designed circuit can get a 2D image with same position resolution and double count rate compared with the original circuit with peak hold and NI card.

宇宙中的一部分天体会发射极其微弱的紫外辐射, 探测这些紫外辐射是对这些天体进行研究的一种重要途径[1]。随着嫦娥三号成功发射, 其有效载荷极紫外(EUV)相机所用的二维位置灵敏光子计数成像探测器在深空探测方面已获得成功应用[2]。此外, 紫外探测在天文观测和电离层遥感等方面也有着重要的应用。针对未来电离层遥感的需要, 本文研制了基于微通道板及感应电荷楔条形阳极(WSA)的远紫外波段二维光子计数成像探测器, 该探测器主要由碘化铯(CsI)阴极、微通道板(MCP)堆、楔条形位置灵敏阳极及相应的位置读出电路组成[3]。其中位置读出电路对来自位敏阳极的微弱脉冲信号进行数据采集、传输及处理, 因此, 其性能好坏直接影响探测器的整体计数率、空间分辨率等性能。

目前所使用的数据采集系统主要由前端模拟电路和每通道采样频率为1 MHz的多通道NI公司的数据采集卡组成, 前端模拟电路包含峰值保持模块, 其作用是将整型放大器输出的高斯型脉冲宽度由大约1.5 μ s展宽到约3 μ s, 以便NI数据采集卡有足够的采集时间获取其峰值[4]。在整个峰值保持期间, 不能再对后面的信号进行采集和处理, 因此必然会漏采在峰值保持期间到来的信号, 同时增加了电路的死时间, 进而降低了探测器系统的整体计数率。为此, 本文设计了一个基于高速模数转换(A/D)芯片和现场可编程门阵列(FPGA)的数据采集电路代替NI公司的多通道数据采集卡, 同时去掉了前端模拟电路的峰值保持模块, 通过一个高速的A/D芯片(65 MHz采样率)对每通道整型放大器输出的高斯型脉冲信号逐点采样后获得其峰值并传输到FPGA内进行处理, 降低了电路的死时间, 因此, 既提高了探测器系统的整体计数率, 又大大降低了位置读出电路的研制成本。

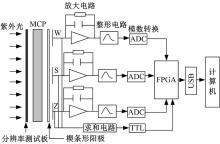

图1为基于楔条形阳极的紫外光子计数成像探测器工作原理框图。外部准直紫外光束透过位于系统前面的分辨率测试板后, 经过阴极转换成光电子。光电子通过MCP堆后不断倍增形成电子云, 电子云落在阳极上面的电阻膜上并且在阳极的3个电极感应形成3个电荷脉冲信号[5]。脉冲信号很微弱, 需要经过一个模拟电路对其进行放大和整形处理[6]。最后, 形成三路脉宽约为1.5 μ s、幅值为0~2 V的准高斯波形脉冲信号, 同时形成一个TTL(Time to live)触发信号[7]。

数据采集电路的高速A/D根据触发信号逐点对高斯脉冲波型进行数据采集, 并且通过滤波和峰值获取等方法将峰值数据通过USB传输到计算机。上位机软件根据一个固定的算法还原出光子的位置, 最后生成图像。获取位置的算法公式为[8]:

式中:(X, Y)为位置坐标; QS, QW, QZ为落在阳极3个不同区域的电荷量, 对应电压脉冲信号的幅值。

如图2所示, 整个数据采集系统由高速A/D芯片、高速FPGA芯片、USB芯片和计算机组成, A/D芯片负责将模拟信号转换成数字信号并送到FPGA中进行处理。FPGA负责数据的处理、对A/D和USB芯片的控制及整个系统的时序控制。USB则是将处理后的数据传送到计算机端, 最后在计算机端经过上位机软件解码还原光子的位置并形成图像。

根据探测器整体计数率的需求, 本文选用美国ADI公司的模数转换芯片AD9226, 该芯片单通道并行输出, 有12位数据转换精度, 最高可以工作于65 MHz采样频率。FPGA选用的是赛灵思公司生产的XC3S500E, 该芯片采用90 nm工艺, 最高工作频率可以达到300 MHz, 并且拥有丰富的逻辑门资源和用户I/O管脚[9]。USB传输芯片使用Cypress公司的CY7C68013A芯片, 这是一款应用广泛的芯片, 能以最高48 Mbit/s的速度进行读写, 完全可以满足本文方案的要求。

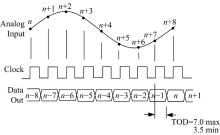

根据A/D数据手册提供的时序(见图3), 芯片在每一个时钟的上升沿进行采样, 并且在7个时钟周期的延迟后输出数据, 使用非常方便[10]。

在数据接收后, 首先经过一个简单的均值滤波算法, 以减小噪声的干扰。首先对进来的8个数据进行求和运算, 然后通过移位实现除法求均值运算, 并且对小数点后的部分进行四舍五入。这种方法在滤除噪声的同时, 并不需要大量的运算, 而且只占用了很少的FPGA片内资源。

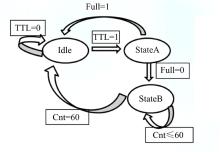

当一个TTL信号到来的时候, 需要对其后的60个数据求得峰值, 这通过一个比较器实现。然后, 依次将这三路12位数据加上标志位后存储到片内生成的一个FIFO(First in first out)之中。整个数据读取的控制逻辑由一个状态机完成, 如图4所示, 其过程具体如下所示。

空闲状态(Idle), 等待TTL触发信号, 当触发信号到来之后(TTL=1)进入StateA。

StateA 判断FIFO是否为满, 如未满进入StateB。

StateB 在计数器未满60时, 往FIFO中写入数据。

USB芯片(CY7C68013A)集成了USB 2.0收发器、智能串行接口引擎(SIE)和增强型8051微处理器。USB芯片进行数据传输的时候, 由FPGA进行外部的逻辑控制。控制过程也由一个状态机完成, 如图5所示, 具体过程如下所示。

空闲等待状态(Idle), 写事件发生时进入State1。

State1 设置端点FIFOADR[1:0], FIFOADR为USB芯片内部端点选择引脚, 然后进入State2。

State2 判断内部FIFO空满状态, 如果未满则进入State3; 否则等待。

State3 把数据输出到数据总线上, 将SLWR置为有效, SLWR为USB芯片中的写使能端, 当其置低有效时可以往数据总线写入数据, 然后进入State4。

State4 若数据没有写完, 则进入State2继续写数据; 若数据已经结束, 则进入空闲状态[11]。

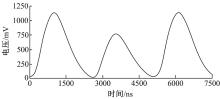

利用本文研制的电路及现有的探测器进行成像试验。首先, 通过其中一个通道对单路信号进行完整的采样后, 输出数据并绘制波形。如图7所示, 对每个脉冲连续采样120个点可以获得比较准确、完整的脉冲波形。从图中可以看出:脉冲的宽度为1.5 μ s, 为近高斯脉冲波形, 并且在加入滤波算法后, 能进一步减小噪声, 获得更准确的波形图像。

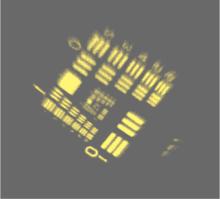

随后进行探测器的空间分辨率测试。通过对空间分辨率板的成像获得试验条件下探测器的空间分辨率。在脉冲整形时间为0.5 μ s、探测器电压为-2400 V, 计数率为36 kcounts/s的条件下对空间分辨率板的成像测试结果如图8所示。结果表明:本文所设计的采集电路能够完成数据的采集并获得较好的图像。与传统采集方法相比, 该电路在实现预期功能并保持分辨率基本不变的条件下, 去掉了峰值保持电路, 优化了电路结构, 并且提高了探测器系统的整体计数率。

最后, 测试探测器的最高计数率。去掉分辨率板之后, 使用紫外光束直接照射探测器, 然后在一定时间内收集光子数据后成像并且计算。产生一个完整的圆形图像的最高计数率即为此条件下的最大计数率。图9为在脉冲整形时间为0.5 μ s、探测器电压为-2400 V时获得的探测器全口径的图像, 此时的计数率为143 kcounts/s, 约为相同条件下使用数据采集卡所能获得的最高计数率的近两倍。

根据紫外光子计数成像探测器对高计数率情况下数据采集的需要, 研制了一套基于FPGA和高速A/D的微通道板光子计数成像探测器高速位置读出电路系统。试验结果表明:该电路性能稳定, 直接通过高速A/D采样芯片对整形放大器输出波形进行多点采样后获取峰值, 去掉了对整形放大器输出波形展宽的峰值保持电路, 减少了脉冲叠加的几率, 提高了位置读出电路的整体计数率及其可靠性, 同时降低了研制成本。

The authors have declared that no competing interests exist.

| [1] |

|

| [2] |

|

| [3] |

|

| [4] |

|

| [5] |

|

| [6] |

|

| [7] |

|

| [8] |

|

| [9] |

|

| [10] |

|

| [11] |

|