作者简介:陈鸣(1985-),男,博士研究生.研究方向:低功耗模拟集成电路设计.E-mail:chenmingl@ime.ac.cn

设计了一种应用于CMOS图像传感器中的低功耗流水线模数转换器(ADC),并采用逐次逼近寄存器(SAR)ADC辅助流水线架构,提出了一种新型全差分环形放大器。与传统的跨导运算放大器(OTA)相比,所提出的全差分环形放大器能效更高。本文采用0.18 μm 1P5M工艺完成电路设计及版图布局,当输入频率为19.94 MHz的正弦信号时,仿真显示ADC的信号噪声失真比(SNDR)为57.8 dB,无杂散动态范围(SFDR)为64.9 dB,最大微分非线性(DNL)为+0.58 LSB/-0.33 LSB,最大积分非线性 (INL)为+0.55 LSB/-0.57 LSB。整个ADC功耗为3.78 mW。

This paper presents a low power pipeline Analog-to-Digital Converter (ADC) used in CMOS image sensor. We propose a new fully differential ring amplifier, and employ a SAR ADC to assist the pipeline architecture. Comparing with conventional Operational Transconductance Amplifier (OTA), the proposed amplifier has higher energy-efficiency. This design is implemented in 0.18 μm 1P5M 1.8 V/3.3 V process. The post-simulation results indicate that it can achieve a maximum differential nonlinearity of +0.58 LSB/-0.33 LSB, a maximum integral nonlinearity of +0.55 LSB/-0.57 LSB, Spurious-Free Dynamic Range (SFDR) of 64.9 dB and Signal-to-Noise and Distortion Ratio (SNDR) of 57.8 dB for a 19.94 MHz input at sampling rate. The total power dissipation of ADC core is 3.78 mW, the FoM of ADC is 148 fJ/conv-step.

CMOS图像传感器(CIS)[1, 2]在消费类电子产品中的应用日益广泛, 对CIS的面积和功耗要求也越来越苛刻。流水线模数转换器(Pipeline ADC)能同时实现较高的速度和精度, 因此在CIS中使用较多。传统的流水线ADC[3]设计中, 余量增益电路(MDAC)是基于闭环负反馈的开关电容电路来实现的, 其中, 跨导运算放大器(OTA)占了模拟域功耗的主要部分。因此, OTA的设计对整个ADC至关重要。随着CMOS工艺的不断发展, 尤其当电源电压降低到1 V以下时, 传统OTA结构的性能已经不能满足低功耗的设计需求。

文献[4, 5, 6]提出了一系列改进方案取代传统OTA。其中Brooks等[4]提出的过零检测(Zero-crossing detecting)技术应用较多, 但这种结构对比较器的失调比较敏感, 其控制电路较为复杂, 难以实现高精度。Hershberg等[5]提出了一种全新的环形放大器(ing amplifier), 然而, 这种放大器对内部失调电压VOS比较敏感, VOS的变化可能导致环形放大器震荡。Lim等[6]精简了环形放大器的结构, 采用电阻自偏置VOS, 并使用高阈值器件, 大大提高了环形放大器的鲁棒性, 但这种结构的电源抑制特性较差, 且单端工作时, 系统的共模抑制能力以及偶次谐波失真都比全差分结构差。为克服以上问题, 本文提出了一种新型全差分环形放大器, 并对所提出的结构作了仿真, 然后设计了一种10 bit 40 MS/s流水线ADC, 验证了本文的可行性。

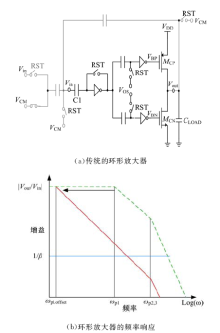

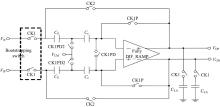

简单的环形放大器结构如图1(a)所示, 其频率响应如图1(b)所示, 当Vin接近VCM时, MCP和MCN会进入亚阈值区, 其输出阻抗急剧增大而形成主极点, 同时主极点和次主极点之间频率间隔迅速增大, 使系统的相位裕度也变大, 从而系统趋于稳定。由于放大器的输出级工作在亚阈值区, 消耗电流极小, 且输出阻抗大, 这使放大器的开环增益能达到80 dB以上, 可满足10~12位的精度要求; 同时, 由于充放电速度快, 所以能满足高速应用。

然而, 这种放大器的工作强烈依赖于内部失调电压VOS, 文献[5]中VOS工作在50~100 mV。VOS过小, 即VBP和VBN相差较小, MCP或MCN进入线性区, 输出阻抗变小, 主极点与次主极点频率接近, 放大器可能会出现阻尼震荡; VOS过大, MCP或MCN可能会进入截止区, 则放大器的带宽急剧降低, 不能在指定的时间内完成建立。当考虑PVT因素时, VOS可能超出正常工作范围, 放大器工作会变得异常。

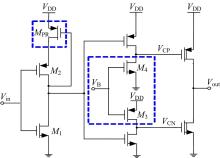

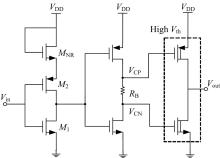

为解决图1中的问题, 同时扩大VBP和VBN的工作范围, Lim等[6]给出了一种解决方案并简化了放大器的结构。如图2所示, 它在第二级反相器的输出端引入了电阻RB, RB两端的电压差VOS(即VCPVCN)作为内部失调电压; 同时, 在输出级引入了高阈值器件。由环形放大器的工作原理可知, 只要VOS满足:

| 图2 文献[5]中的环形放大器Fig.2 Ring amplifier in literature [5] |

则MCN和MCP工作在亚阈值区, 式中VTHN和VTHP分别为MCN和MCP的阈值电压。由于采用了高阈值器件和自偏置VOS, VTHN和|VTHP|都较大, 条件(1)更容易成立。因此, 这种结构能提高环形放大器的鲁棒性; 此外, 高阈值器件的引入也提高了输出阻抗, 使环形放大器的开环增益得到进一步提升。MNR的引入是为了功耗和噪声的折中。

尽管图2中的结构进一步优化了环形放大器的稳定性, 但电源抑制和共模抑制能力依然较差。对于二极管接法的MNR, 电源的扰动可直接作用到栅极, 也会产生相同的扰动, 因此, 放大器对来自电源的扰动几乎没有抑制作用; 其次, MNR上的压降VGS较大, 文献[6]中采用65 nm工艺, PMOS的VGS的典型值约为0.35 V, 对于1.2 V的电源电压, 输入管的跨导和电流可较好的折中; 但对于180 nm工艺, 这个VGS的值约为0.7 V, 要获得同样大小的跨导, 输入管的尺寸会变得很大, 而过大的尺寸会增加输入寄生电容, 进而对ADC的精度和速度造成影响, 恶化放大器的性能。此外, 电阻RB的引入虽然能产生内部失调电压, 但集成电路中电阻的制作精度较差, 其绝对误差可以达到± 20%, 这会使图2中的VOS变化较大, 此时, 输出级可能会脱离亚阈值区而进入线性区, 环形放大器将不再正常工作。

由图2还可以看到, 电源上的扰动不再直接作用于M2的源极, 放大器对电源的扰动有一定的抑制作用, 从而提高了第一级的电源抑制能力; 更重要的是, 由于MPR的负反馈作用, 第一级反相器的输出电压更稳定, 提高了系统的共模抑制能力。MPR工作在线性区, 引入负反馈后, 第一级反相器的等效跨导为:

式中:gm1、gm2分别为M1和M2的跨导; go3为MPR的导纳, go3的值和gm2的值近似相等。合理调节MPR的尺寸即可调节第一级反相器的电流和带宽, 从而优化第一级反相器的速度和功耗。实际设计时, 为了获得更高的速度, M1和M2的宽长比(W/L)会尽可能大, 考虑到PMOS的迁移率较大, 一般取M2的尺寸为M1的3到4倍以使反相器的翻转尽可能在中间电平。

原有的电阻RB被共源极接法的MOS管M3和M4取代, VB是它们的偏置电压, 本文直接取VB为放大器的输出共模电压VCM(0.5VDD)。放大器的第二级被劈裂成两个共源放大器。这种结构的好处是由MOS有源负载直接产生偏置电压VCP和VCN, 其内部失调电压VOS不再受集成电路中电阻制作工艺的影响。由于M3和M4单独使用了偏置电压VB, 第一级的输出节点并未增加额外的寄生电容, 不会降低放大器的带宽; 此外, 由于输出级工作在亚阈值区, VCN较小(接近于VTHN), VCP较大(接近于VDD-|VTHP|), 因此, M3和M4的尺寸都较小, 只有微弱的上拉和下拉能力, 流过它们的电流也较小, 满足低功耗设计要求。为了降低第二级的电流, M3和M4的沟道宽度取为最小值220 nm, 实际流过每个共源级的电流约30 A。第一级反相器的带宽直接决定了放大器的速度, 因此, 第一级反相器消耗的电流较大; 第三级的电流消耗极小, 所以输出级的尺寸也较小, 实际取高压管的最小沟道长度0.35 m, 为了兼顾放大器的稳定性, 其NMOS沟道宽度仅取为1 m, PMOS的沟道宽度为3 m。

图3所示的环形放大器由于是单端输入单端输出, 它始终带有单端结构的缺点, 如偶次谐波失真大、抗噪声能力弱等。为了克服这些问题, 本文进一步提出了一种全差分环形放大器, 如图4所示。相比于文献[5, 6]中用两个单端放大器的伪差分结构, 本文提出的全差分结构对称性更好。该放大器的第一级引入了NMOS尾电流源, 使输入对实现差分化, 即形成差分输入、差分输出的环形放大器。由于线性区的MPR对第一级输出电平具有稳定作用, 故而第一级无需额外的共模反馈, 第二级增益较低, 也不需使用共模反馈, 第三级的输出共模反馈采用开关电容电路(SC-CMFB)[7], 反馈控制端VFB即是尾电流源的栅极。CK1和CK2为两相不交叠时钟, VCM为放大器的输出共模电压, VB的值与VCM相同, VBN由基本的电流镜偏置产生。输出级使用了3 V高阈值器件拓展VOS的范围, 在1.8 V的电源电压下, 仿真得到VOS约0.3 V。

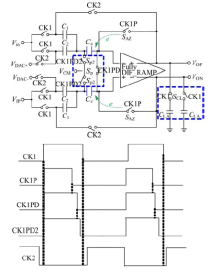

开关SAZ在断开时会对电容CC注入电荷, 这些电荷会表现为输出失调。为消除这一失调, 本设计引入了开关Sp, 它由CK1PD控制, 采用适当的时序, 可以消除SAZ引入的失调。图5给出了MDAC中各项时钟的时序图, 采样结束时, 调零开关SAZ首先断开, 然后Sp断开, 这使环形放大器输入端的电位始终近似相等, 由开关SAZ引入的失调被消除。此后, 由CK1PD2控制的开关Sp2断开, 最后CK1再断开, 由于采样开关断开时的注入电荷没有泄放通路, 不会对电路产生影响。为了观察MDAC在不同输入幅度时的增益变化, 仿真验证了一些直流值, 仿真结果可以看出, MDAC能精确地倍乘输入信号, 其输出误差小于0.5 LSB(0.976 mV)。

| 表1 MDAC仿真结果 Table 1 MDAC simulation result |

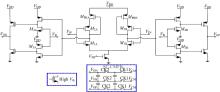

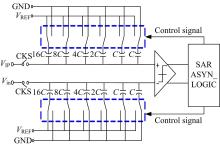

本节采用所提出的放大器结构设计了一种10 bit 40 MSample/s 流水线ADC。图6是流水线ADC的整体架构。为了降低ADC的整体功耗, 尽可能少地使用放大器, 流水线的后6级使用了一个6 bit异步SAR ADC取代了传统的1.5 bit/stage结构。为消除孔径误差, 本设计使用了采样保持器(SHA)。SHA的电路结构如图7所示, 采样电容为400 fF, 并采用电容翻转式结构, 由于反馈系数较大, 该结构比电荷重分布式更节省电流。采样开关使用自举开关, 以获得更低的导通电阻和更好的线性度, 采样保持器静态消耗电流约320 A。ADC的首级采用了2.5 bit, 其结构如图8所示, 它能提高系统的线性度并降低整体功耗, 其采样电容为400 fF, 消耗静态电流约440 A。由于流水线每级的容忍误差逐级加大, 分配第二级和第三级的静态电流分别为240 A、180 A, 采样电容均为360 fF。Cc的取值不宜过大, 也不宜过小, 文献[6]指出Cc+CLA> 2C1才能保证环路的稳定性, 本文取Cc为200 fF。

本设计中6 bit SAR ADC的结构如图9所示, 它采用了改进的单调开关时序, 能进一步降低功耗。

与传统的单调开关[8]不同的是, 当CKS为高, 电容对输入信号采样时, 上下电容阵列只有最高有效位(MSB)电容连接至VREF, 其余位均连接至GND, 采样后直接进行比较并得到最高位输出结果, 其余位均采取先比较后置位的原则逐位得到输出码。这种工作机制使 DAC 中的电容缩减了一半, 且每次的比较过程中只有一次开关动作, 大大减少了动态功耗; 这种接法的另一个优点是减少了比较器输入共模电平的变化, 从而降低比较器的系统失调。图中SAR ADC的总电容个数为64C, 考虑到电容的面积和前级的驱动能力, 单位电容C的取值不能过大, 小的电容虽然能提高速度, 但会影响精度, 本设计采用18 fF的MIM电容作为单位电容, 上下电容阵列的总电容值为1.152 pF。

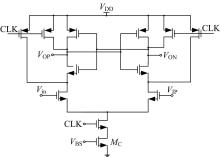

图10 6bit SAR ADC使用的比较器结构。为了降低比较器的输入失调, 本设计在尾电流源中采用了共源共栅结构。共源管MC由偏置电压VBS控制, 由于MC工作在饱和区, 其漏源端电压VDS的变化对电流的影响较小, 使输入对管的过驱动电压保持恒定, 从而降低输入失调的影响。

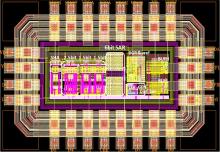

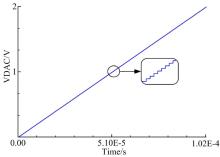

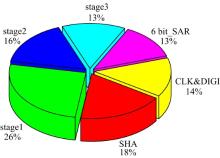

本设计基于 0.18 μ m 1P5M1.8 V/3.3 V混合信号工艺构建了一个10 bit 40 MS/s流水线ADC, 图11为ADC的整体版图, 芯片面积为0.235 mm2。本设计提取出版图的寄生参数, 然后进行电路后仿真。本文首先仿真了ADC在输入斜坡信号时输出性能。当输入一个满量程(-1 V至+1 V)的斜坡信号, 为使每个LSB被采样次, 上升时间设定为102.4 s(即1024× 25 ns× 4), 再利用理想的10 bit DAC还原出ADC的量化结果。图12给出了DAC的输出瞬态曲线, 它是0~2 V的1024级台阶, 每级台阶的高度为1 LSB (1.953 mV), 且每个code均匀出现, 这说明ADC的功能完全正常。图13给出了ADC各级的(平均)功耗分布饼图, 它与之前的电流预算值基本吻合。

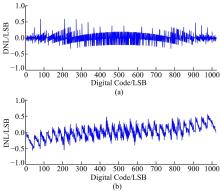

当差分输入一个频率为3.964 MHz, 幅度为VPP=2 V的正弦波信号, 采样频率为40 MHz, VDD=1.8 V时, 采样2048个数据点, 利用Matlab分析ADC的静态特性和动态特性。如图14所示, DNL最大值约+0.58 LSB/-0.33 LSB, INL的最大值约+0.55 LSB/-0.57 LSB, 对于图像传感器来说, 这样的DNL和INL特性满足无失码的要求。从图15所示的ADC动态特性仿真结果可以看出, 在输入为低频(Fin = 3.964 MHz)时, ADC的SFDR为76.9 dB, SNDR为60.2 dB, 有效位数约为9.71 bit; 在输入接近奈奎斯特频率(Fin = 19.94 MHz)时, ADC的SFDR为64.9 dB,

| 图15 输入频率分别为3.964 MHz和19.94 MHz的动态特性仿真结果Fig.15 ADC dynamic characteristic simulation result for 3.964 MHz and 19.94 MHz |

SNDR为57.8 dB, 有效位数约为9.31 bit。ADC CORE的平均动态功耗约为3.78 mW。ADC的FoM定义为:

式中:Power为功耗, fs为采样频率。

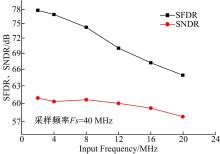

本设计的FoM值约为148 fJ/conv-step。图16给出了ADC的SNDR、SFDR与输入频率之间的关系, 可以看到, 随着输入频率的增加, SFDR也随之下降, 当输入频率增大至奈奎斯特频率附近时, SFDR和SNDR的值最低; 这是因为在高频输入时, SHA的性能下降较快, 导致ADC的整体性能下降, 尽管如此, 这样的动态性能满足设计指标。表2对ADC的各项性能进行了总结, 并给出了ss corner和ff corner下的性能指标。

| 表2 ADC性能总结@19.94 Mhz Table 2 ADC performance summary |

表3列出了本设计和近年来文献中流水线ADC的性能指标。由表3可知, 本文中ADC的性能虽然低于部分文献的FoM值, 但本文采用较落后的0.18 μ m工艺, 相同电流消耗的下, 本文的FoM值会更高。

| 表3 近年报道的ADC性能对比 Table 3 Performance comparison with recent reported pipeline ADC papers |

本文提出了一种新型全差分环形放大器, 并利用提出的放大器设计了一种10 bit40 MSample/s的流水线ADC, 在提取了版图的寄生参数后进行了后仿真。仿真结果显示本文所提出的全差分放大器功能完全正常, 本设计中的流水线ADC性能满足CMOS图像传感器的应用需求, 可以投片生产。

The authors have declared that no competing interests exist.

| [1] |

|

| [2] |

|

| [3] |

|

| [4] |

|

| [5] |

|

| [6] |

|

| [7] |

|

| [8] |

|

| [9] |

|

| [10] |

|

| [11] |

|

| [12] |

|