作者简介:丁宁(1990-),男,博士研究生.研究方向:CMOS集成电路设计.E-mail:715173723@qq.com

随着高速CMOS图像传感器分辨率和帧率的大幅度提升,无论在数据传输带宽方面还是缓存容量方面都需要图像采集系统能够应对巨大的实时数据量来满足使用要求。基于此,本文提出了一种基于现场可编程门阵列(FPGA)和USB 3.0的高速CMOS图像传感器的数据采集系统实现方式。本文依次从系统电路硬件设计、FPGA和USB 3.0芯片软件功能设计以及上位机软件设计进行阐述,最后对系统进行整体调试并给出了实验结论。测试结果表明本系统能够最大化利用USB 3.0芯片的传输能力,同时实现图像接收过程的零误码率。因此,该系统可较好地满足目前高速高分辨率CMOS图像传感器对数据采集的数据实时性和准确性要求。

Due to the rapid improvement of the resolution and frame rate of the high-speed CMOS Image Sensor (CIS), image acquisition systems claim a higher level requirement for data bandwidth and cache capacity to dealing with the huge amount of real-time data from the sensor. According to this situation, this paper presents an implementation method for high-speed CIS data acquisition system based on FPGA and USB 3.0. The acquisition system is constructed by following parts: design of system hardware circuit, FPGA and UBS 3.0 software design, PC operation software design, system testing and debugging and measurement results. The results indicate that this system can use the maximum capacity of UBS 3.0, meanwhile, achieve zero Symbol Error Rate (SER) during the image reception process. Therefore, the system satisfies the requirement of real-time ability and accuracy of data for the current high-speed resolution CIS.

随着CMOS图像传感器的应用日益广泛, 其性能也得到了巨大提升, 尤其在高帧频、高分辨率等方面表现的极为明显。CMOS图像传感器指标的提升势必导致产生的数据量变得非常庞大, 比如国内辰芯公司最新推出的GMAX3005系列CMOS图像传感器[1], 其分辨率达到了1.5亿像素, 其单张全幅图片产生的数据量可达到200 MB以上, 这就要求数据采集系统必须具备数据快速读取的能力, 以便系统能够在最短的时间内处理大量数据, 同时把数据传到上位机进行显示或者处理的后续工作。这就要求高速数据采集系统在各个环节都必须满足处理高速数据的要求, 包括数据接收、数据缓存、数据发送等[2, 3, 4]。

数据接收方面, 现场可编程门阵列(Field programmable gate array, FPGA)基于查找表结构, 采用并行处理方式, 可以利用其内部集成的IP核进行数据处理或者与外围器件进行连接, 所以在高速数据采集系统中应用广泛。数据缓存是高速数据采集系统的重要部分, 高传输速率和大存储容量的特性需要使用SDRAM才能满足系统的设计要求。但是由于SDRAM复杂的接口和较高的时序要求以及同步刷新等特点使其在应用上比较麻烦。不过随着FPGA的发展, 其内部集成了控制SDRAM的IP核, 使得开发者可以比较容易实现对SDRAM的控制。数字接口的传输速度制约着整个高速数据采集系统的性能, 集高可靠性和高速度特性于一身的USB 3.0接口正在逐步替代目前许多CameraLink接口的应用, 其在成本和普及性方面的优势更使其给机器视觉应用带来了更好的解决方案[5, 6, 7, 8]。

本文采用高性能FPGA作为主控芯片进行数据采集过程的整体调度; 利用DDR2 SDRAM芯片进行图像数据缓存; 上位机采用LabVIEW实现图像数据实时显示。经验证, 该方案可以有效实现高速CMOS图像传感器图像数据的实时采集。

系统上电之后, FPGA程序通过I2C协议对CMOS图像传感器进行配置。芯片初始化以后产生像素数据, 行有效信号和帧有效信号通过采集板的通用输入输出接口传输到FPGA内部, 然后FPGA通过DDR2 SDRAM控制IP核程序将像素数据传输到DDR2 SDRAM进行缓存, 缓存一帧图像后对该图像进行读取并发送到USB 3.0芯片接口, 最后USB 3.0芯片将接收到的并行多路数据按照USB协议打包并发送到上位机。USB 3.0芯片工作模式设置为Slave FIFO, 接口位宽设置为32 bit。上位机界面利用LabVIEW语言开发, 通过VISA工具编写USB 3.0驱动, 建立连接以后可以与USB 3.0芯片进行通信, 包括数据的接收和发送。上位机将接收到的图像数据进行缓存和重组, 转化为图像之后进行显示。

在本设计中, 为了方便对采集系统的性能进行测试, 利用FPGA开发板模拟CMOS图像传感器芯片产生测试图像数据, 系统对该数据进行接收, 通过调整测试数据产生速率来对系统进行优化和调整, 以达到最佳性能。

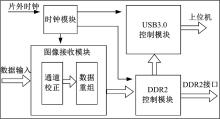

图1为高速CMOS图像传感器数据采集系统的硬件原理图。 从功能上划分, 系统主要由3部分组成:CMOS图像传感器、高速数据采集板和上位机。不同于CCD图像传感器, 由于CMOS图像传感器内部集成有模数转换器, 所以CMOS传感器输出的是多路数字信号, 可以由FPGA直接进行接收。

根据CMOS图像传感器的输出数据格式, 可以通过编写FPGA程序产生相同格式的数据来模拟CMOS图像传感器的输出信号, 通过调整输出像素时钟频率和行有效、帧有效信号波形可以得到对应不同格式的图像数据, 利用这种方法可以验证采集系统对于不同分辨率CMOS图像传感器的接收能力, 本系统在验证过程中采用了此种方法。

FPGA作为整个数据采集系统的主控芯片, 在性能和资源方面需要满足构建多级缓存的数据处理需求。Xilinx公司Spartan-6系列芯片具有较高性价比, 选用XC6SLX45-2FGG484C型号的芯片, 该芯片具有43 661个逻辑单元, 最大块存储资源为2088 kbit, 片内资源可以满足需求, 该芯片同时具有存储器管理模块, 可以方便地进行DDR2动态内存控制。

FPGA配置方式采用SPI主从模式, 上电后SPI-Flash芯片引导程序启动, 选用芯片型号为M25P16, 芯片中存储FPGA程序和用户配置文件, 用户配置文件采用十六进制文本形式, 主程序配置完成后读取配置文件, 进行工作模式设定。

USB 3.0芯片选用Cypress公司新一代产品CYUSB3014-BZXI, 该芯片具有可完全配置的并行通用可编程接口GPIF II, 可与FPGA直接连接。芯片集成32位ARM926EJ-S微处理器, 具有强大的数据处理能力, 另外该产品采用特殊架构, 使从GPIF II到USB接口的数据传输速度可达320 Mbit/s。

DDR2 SDRAM芯片选用Micron公司产品型号为MT47H64M16HR-3IT, 两片DDR2 SDRAM芯片并联使用, 并联后位宽为32 bit, 数据时钟为400 MHz。

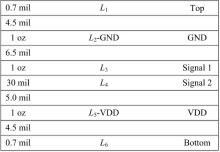

图2为高速数据采集板PCB板层结构和设计参数。本设计采用6层结构(L1~L6), 其中Top、Signal1、Signal2和Bottom是四层信号线层; GND为参考地层; VDD为电源层。PCB整体厚度设计为 62 mil(1.57 mm), PCB材质选用能够较好控制尺寸和介质层厚度的FR-4, 在频率为100 MHz情况下, FR-4介电常数平均为4.2, 根据该常数来实现对信号线的阻抗匹配。本设计中, 单端信号线阻抗匹配设计为50 Ω , 差分信号线阻抗匹配设计为90 Ω 。

FPGA芯片是整个系统的主控制芯片, 负责与USB 3.0芯片和DDR2芯片等外围器件的通信, 所有图像数据的接收、发送、缓存等功能都利用FPGA芯片来进行控制。图3为FPGA程序框图。

对所采用的CMOS图像传感器芯片进行工作模式配置, 待图像传感器初始化完毕, 根据其产生的像素时钟, 行有效信号和帧有效信号来接收图像数据。图像数据采集之前, 首先需要对接收数据的多路通道进行校正, 以保证数据采样的准确性。将FPGA接收到的图像数据发送到DDR2 SDRAM中, 根据系统时序对DDR2 进行数据写入和读出操作。在对DDR2进行操作之前首先需要完成初始化工作。与USB 3.0芯片进行通信并进行数据传输, 将DDR2 SDRAM缓存的图像数据通过USB 3.0高速数据接口传送到上位机软件进行显示。

(1)DDR2 SDRAM控制IP核生成方法

Core Generator是用来生成IP核的EDA工具, 本文DDR2控制器就是由Core Generator生成, 然后应用到工程文件中。生成IP核的过程只需按照工具提示即可完成[9]:首先选择FPGA器件型号和封装类型; 接着按步骤依次选择生成IP核所在的Bank、DDR2 SDRAM频率和器件型号, 如果列表中没有可以选择的器件型号可以按自定义时序生成配置文件; 然后对DDR2 SDRAM芯片的信号接口进行配置, 包括阻抗匹配、端口驱动能力、端口属性、地址映射以及保留有特殊功能的引脚配置等, 比如RZQ引脚和ZIO引脚; 所有配置完成以后, 得到信息总结列表, 经过确认配置无误以后, 即可开始生成IP核文件。在配置IP核的时候可以选择生成的文件类型, 包括VHDL文件、Verilog文件和Schematic文件, 为了方便对工程文件的调用和修改, 本文选择生成的文件类型为Verilog文件, 在自动生成的文件夹中, 可以查看生成的代码文件。

(2)多路数字通道校正方法

FPGA在接收数据时根据采样时钟边沿判断输入信号的高低电平, 如果发生采样时钟边沿与数据边沿重合或者距离数据边沿很近从而无法保证满足建立时间和保持时间的情况, 则采样得到的数据会出现错误, 这一现象在信号频率比较高的时候更容易发生, 所以理想的情况是采样时钟在数据高电平或者低电平持续时间的中间进行采样, 以保证采样得到的数据的准确性。本系统需要对多通道高速数字信号进行采集, 所以有必要增加多路通道校正模块, 以保证接收的数据准确[10]。

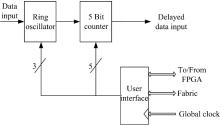

Spartan-6系列FPGA芯片内每个IO模块都包含可配置延迟单元, 可以用来配置IO接口的输入延迟、输出延迟或者在两者之间进行切换。图4是延迟模块的基本结构。延迟时间根据每个延迟单位时间长度和延迟单位数目共同决定, 不同型号芯片对应的延迟单位时间不完全相同, 对于固定芯片来说, 延迟时间由延迟单位数目决定。本系统采用的FPGA芯片延迟单元的延迟单位数目共有8位, 所有延迟单位数目可以配置为0~255之间的任何数值。可配置8位数据中的低3位用来控制起振时刻, 同时输出信号对该5位计数器进行记录, 输出信号延迟在可配置的0~7之间任意个延迟单位之后。5位计数器就是预设的8位数据的高5位, 在输出信号转换为原始信号之前从0~31不断循环计数。正是利用这种方法实现了将输入信号延迟0~255个延迟单位然后输出。

本系统的通道校正方法利用状态机来实现, 校正的思路是, 首先选定一个数据传输通道并判断待校正信号的上升沿; 然后判断待校正信号的下降沿, 根据上升沿和下降沿所在延迟时刻计算出信号电平稳定持续时间的中间时刻, 将该值设置为该通道的延迟数值。具体实现方法是, 首先利用串并转换器降频, 然后进行位校正, 连续采集数据进行对比, 直到多组数据相同并稳定。接着进行字校正, 将采样数据与训练字进行对比, 直到完全相同并稳定时字校正结束。最后进行通道校正, 多个通道依次进行位校正和字校正工作, 直到全部通道校正之后将校正结果上传到上位机进行观察[11]。为了节省资源, 校正过程采用各通道轮流校正, 并没有采用所有通道同时校正的方式。

(3)USB 3.0通信模块设计

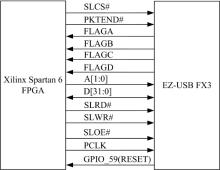

本系统中, USB 3.0控制芯片的功能是负责将接收到的图像数据发送到上位机, 同时接收上位机发出的控制命令信号, 以协处理器的模式工作。作为从器件, USB 3.0芯片主要功能是进行高速数据的传输, 最高支持32位并行数据总线, 接口频率最高达到100 MHz。图5是USB 3.0芯片作为从处理器时的接口。

FPGA程序设计中用到多个状态, 状态的跳转利用状态机来控制, 本系统中用到的通信模式是回流传输模式, 所以需要根据与USB 3.0芯片通信过程用到的状态来设计。图6是FPGA程序的状态机跳转图。在编写FPGA控制USB 3.0芯片程序时, 首先需要按照USB 3.0工作模式确定控制模块接口信号; 然后根据USB 3.0芯片读写时序来编写Verilog程序。

CYUSB3014芯片工作方式取决于本身固件程序的设定。本系统中, USB 3.0控制芯片作为协处理器工作, 工作模式设置为Slave FIFO, 工作模式设置利用GPIF Designer软件实现, 接口属性根据实际需求做调整, 同时将更新后的配置集成到固件中, 然后将更新后的固件程序下载到USB 3.0芯片。

首先设置接口控制信号、数据位宽和标志位属性。在设计中, 将数据传输位宽设定为32 bit, 将FLAGA配置为Current_thread_DMA_Ready模式, FLAGB配置为 Current_thread_DMA_WaterMark模式。FLAG信号可以设置为满/空FLAG和局部FLAG, 但是局部FLAG仅用于决定传输结束的时间, 所以必须在开始传输时对满/空FLAG进行监控。这意味着, 局部FLAG无法单独使用, 而必须和满/空FLAG相结合。配置局部FLAG的另一点是设定固件中的标志水印值, 水印值决定何时激活局部FLAG。设定水印值得方法是根据计算公式来确定:当进行写FIFO操作时, 时钟沿到来后写入的数据字数=水印× (32/总线宽度)-4; 当进行读FIFO操作时, 时钟沿到来后读取的数据字数=水印× (32/总线宽度)-1。

然后, 设计工作状态机和时序, GPIF Designer软件提供了非常方便的开发环境, 只需要用户按照自己的需求来添加或者修改状态及时序, 在状态机和时序设计完成以后利用软件编译即可生成固件程序需要的头文件。

上位机是整个系统与用户交互的部分, 在本系统中主要负责控制图像数据采集的开始和结束, 将采集到的图像数据恢复成图像并进行显示, 同时可以观察FPGA采集数据之前的通道校正情况。软件设计语言采用LabVIEW。

LabVIEW可以选用不同的方案与USB通信[12]。第1种是调用动态链接库文件, 提取库文件函数的方法。首先编写动态链接库DLL文件, 然后调用API函数接收数据并存在缓冲区中, LabVIEW通过调用DLL文件读取缓冲区可以将接收到的USB数据进行读写。这种方法的优点是可以实现USB接口免驱的特点, 可移植性好, 但是缺点是对DLL生成文件依赖性强, 如果DLL文件中的函数运行不稳定就会导致LabVIEW程序崩溃。另一种方法是调用NI-VISA子程序控件的方法。这种方法是与USB设备底层直接通信, 所以稳定性好而且不受平台限制, 只需使用控件内的打开、关闭、读和写等模块就能实现对USB设备的简单读写。这种方法的劣势是与设备通信之前必须首先安装USB设备的驱动。考虑到系统测试阶段程序稳定性的要求, 本系统选用第2种方法。

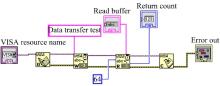

VISA开发包中有可以与底层硬件直接通信的模块, 只需要通过4个节点即可完成对USB设备的读写, 这4个节点的功能分别是打开并建立资源与计算机的通信管道、关闭资源与计算机通信管道、将缓冲区的字符或者数据发送到设备以及将设备中的字符或者数据读到缓冲区。图7就是利用这4个节点实现了LabVIEW与USB设备之间的批量数据收发功能。

LabVIEW作为一个软件平台, 其内部集成了多种软件包, 根据软件包的不同可以实现多种功能。比如用于数据采集和通信的NI-VISA, 用于机器视觉开发的NI-Vision等。在4.1节中对数据的采集就是用到了NI-VISA的功能。本节中, LabVIEW的功能是需要将接收到的图像二进制数据恢复成图像并通过窗口显示出来。在NI-Vision开发包中集成了大量关于图像分析和处理的模块可供调用, 在使用时, 只需要根据数据流的传输过程和相关数据类型来确定使用哪些功能模块。

由于USB传输是串行传输模式, 采集到的 CMOS图像数据是以串行数据流的形式传送到上位机, 所以需要对数据进行重组才能恢复出原始图像。首先需要根据数据量大小建立数据缓存, 用来寄存图像数据; 然后根据CMOS图像传感器的发送格式将数据转化成灰度图或者其他格式图像。在本设计中, 像素输出格式是RGB565格式, 即每16位数据代表一个像素点, 所以按照16位数据转化一次的格式将缓存数据进行转化, 转化后的图片最终为灰度图像文件。CMOS图像传感器分辨率为640× 480, 所以转化数据的时候当计算一帧图像完所有像素点后将缓存清空, 然后继续进行下一帧的转化。

硬件系统检查完毕以后, 在板上对USB 3.0引导方式进行配置, 本设计中先用I2C引导, 如果不成功则用USB进行引导的方式, 具体配置方法是将配置引脚PMODE[2:0]的值设定为F1F, 也就是将PMODE1引脚接高电平, 另外两个引脚悬空。然后检查19.2 MHz晶振和各部分供电电压, 一切正常的情况下开始安装USB 3.0驱动文件。驱动完成以后将USB芯片通电, 这时PC会对USB设备进行枚举操作, 然后就可以进行数据传输。

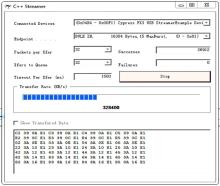

Cypress公司官方提供的SDK中含有测试USB接口性能的软件, 其中测试传输速度的是Streamer软件, 本次设计中采用该软件对整个系统的数据传输速率进行测试。测试方法是利用Xilinx公司的核心板来模拟CMOS图像传感器的时序发送图像数据, 数据位宽设为8 bit, 利用LVDS信号传输, 数值初始值设为0, 每个像素时钟加1。利用数据采集板对8路LVDS信号进行接收, 然后用Streamer软件进行速度测试。测试结果表明, 该系统数据传输速率可以达到320 MByte以上, 并且能够基本保证数据稳定。图8是数据传输速率测试图。

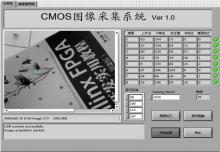

首先将整个系统各部分连接, 包括图像传感器、数据采集板和PC。系统检查正常后将系统通电, 利用JTAG下载器将FPGA程序下载到PROM配置芯片中, 配置PROM的同时可以连同FPGA一起进行配置。由于已经在PC上安装了USB 3.0驱动, 所以此时电脑会识别出USB设备, 然后利用Control Center软件配置USB 3.0芯片, 由于USB启动方式设置为I2C优先配置, 所以需要将固件程序下载到I2C配置芯片中, 也就是24LC256芯片。所有程序下载以后, 将整个系统复位, 等待系统进行自动配置, 包括CMOS图像传感器初始化, USB固件下载等, 然后就可以进行上位机的操作。首先对数据传输通道进行校正, 如果校正结果正常就可以开始进行数据采集。图9是采集系统上位机显示界面。

本文设计了应用于CMOS图像传感器的高速数据采集系统。该系统以并行处理能力强大的FPGA作为主控芯片; DDR2芯片负责高速数据缓存或者存储; 利用USB3.0芯片作为接口芯片负责与上位机进行通信。测试结果表明, 该系统稳定传输速率能够达到320 Mbit/s, 同时能够对CMOS图像传感器进行图像采集, 基本能够满足大部分采集需求。该系统的另一个特点就是灵活性非常好, 采集板供电采用5 V直流电源, 上位机软件利用LabVIEW设计完成可以方便地封装成可执行文件, USB接口本身具有免驱的特性, 所以该系统有非常广泛的应用空间。

The authors have declared that no competing interests exist.

| [1] |

|

| [2] |

|

| [3] |

|

| [4] |

|

| [5] |

|

| [6] |

|

| [7] |

|

| [8] |

|

| [9] |

|

| [10] |

|

| [11] |

|

| [12] |

|