吉林大学学报(工学版) ›› 2025, Vol. 55 ›› Issue (3): 1072-1081.doi: 10.13229/j.cnki.jdxbgxb.20230566

• 计算机科学与技术 • 上一篇

基于Vitis HLS的FIR滤波器设计及其性能分析

张海龙1,2,3,4( ),杜旭1,2,张萌1,2,张亚州1,2,王杰1,4,冶鑫晨1,4,王万琼1,李嘉1,吴涵1,2,张婷1,2

),杜旭1,2,张萌1,2,张亚州1,2,王杰1,4,冶鑫晨1,4,王万琼1,李嘉1,吴涵1,2,张婷1,2

- 1.中国科学院 新疆天文台,乌鲁木齐 830011

2.中国科学院大学,北京 100049

3.中国科学院 射电天文重点实验室,南京 210008

4.国家天文科学数据中心,北京 100101

Filter design and performance analysis based on vitis HLS

Hai-long ZHANG1,2,3,4( ),Xu DU1,2,Meng ZHANG1,2,Ya-zhou ZHANG1,2,Jie WANG1,4,Xin-chen YE1,4,Wan-qiong WANG1,Jia LI1,Han WU1,2,Ting ZHANG1,2

),Xu DU1,2,Meng ZHANG1,2,Ya-zhou ZHANG1,2,Jie WANG1,4,Xin-chen YE1,4,Wan-qiong WANG1,Jia LI1,Han WU1,2,Ting ZHANG1,2

- 1.Xinjiang Astronomical Observatory,Chinese Academy of Sciences,Urumqi 830011,China

2.University of;Chinese Academy of Sciences,Beijing 100049,China

3.Key Laboratory of Radio Astronomy,Chinese Academy of;Sciences,Nanjing 210008,China

4.National Astronomical Data Center,Beijing 100101,China

摘要:

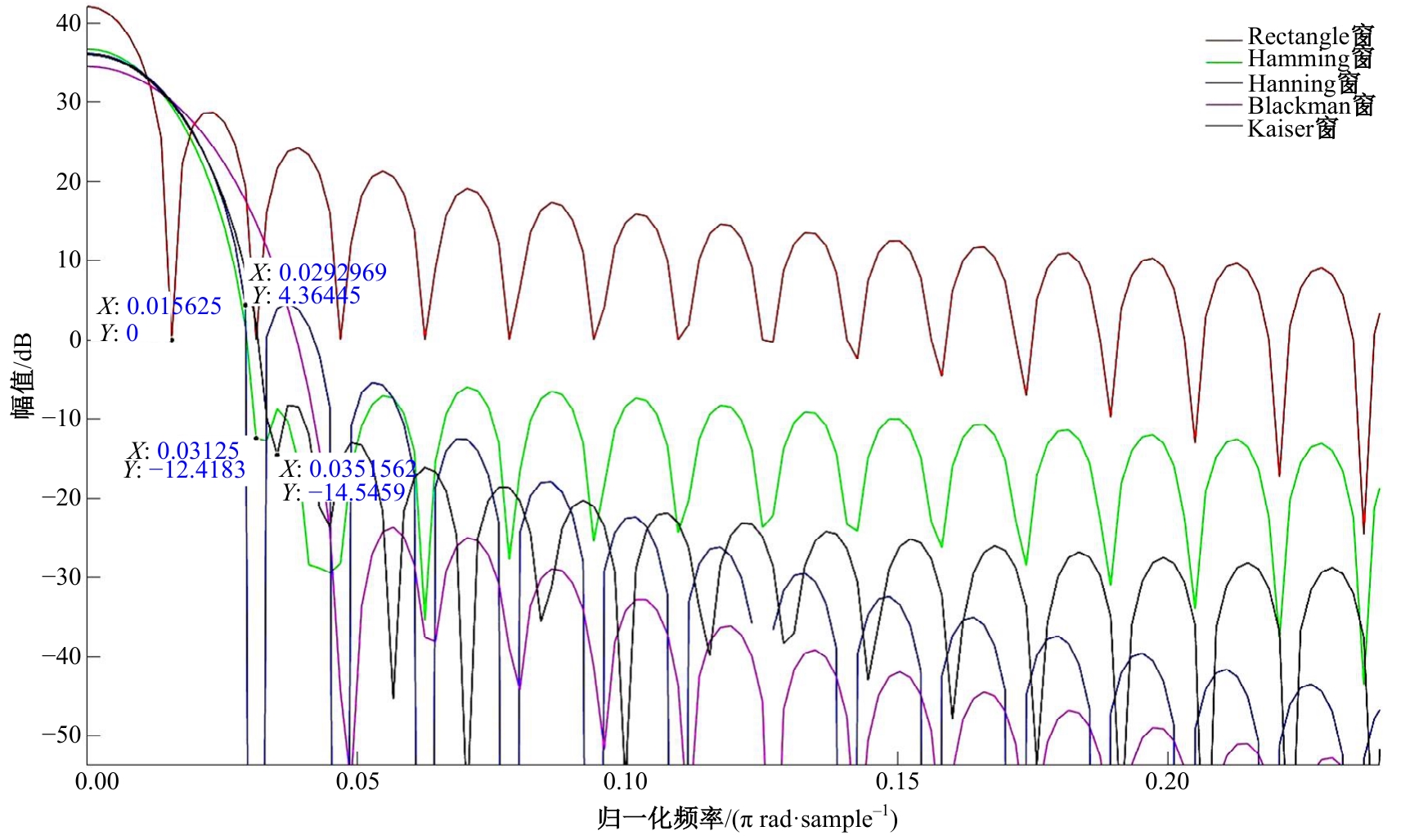

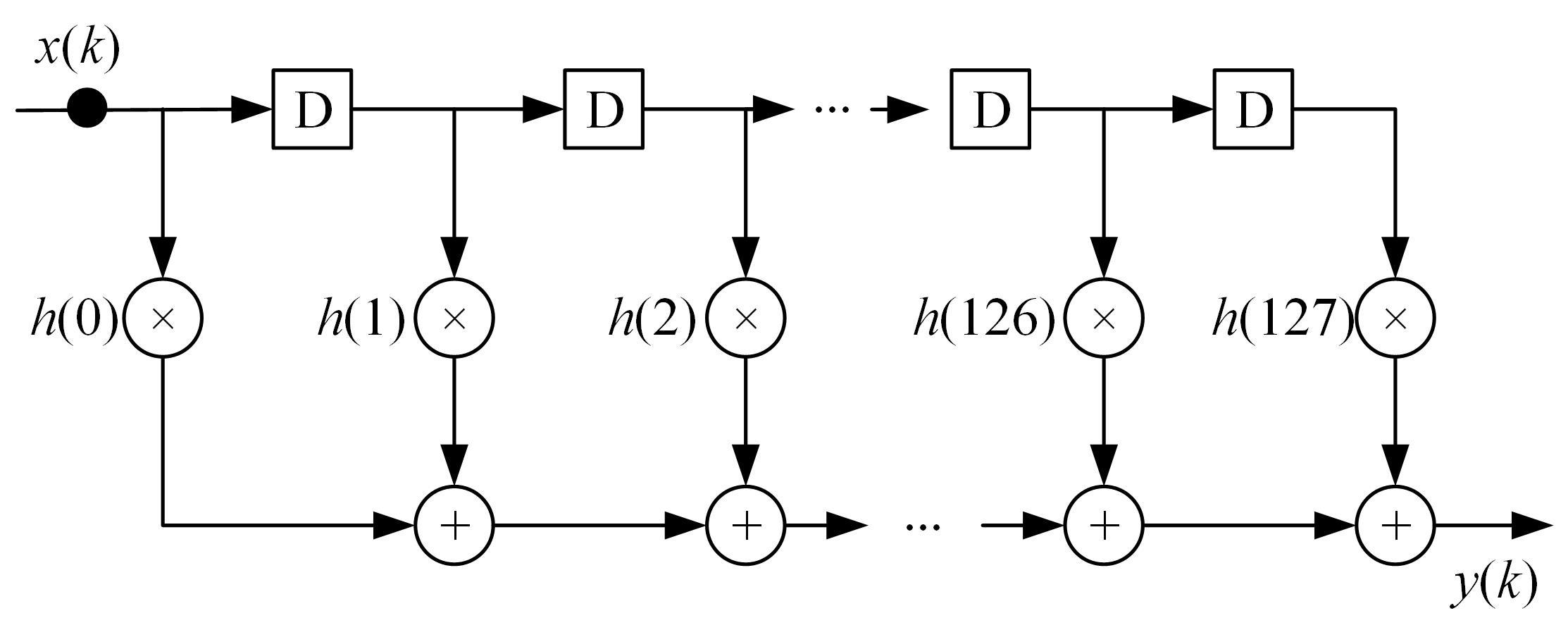

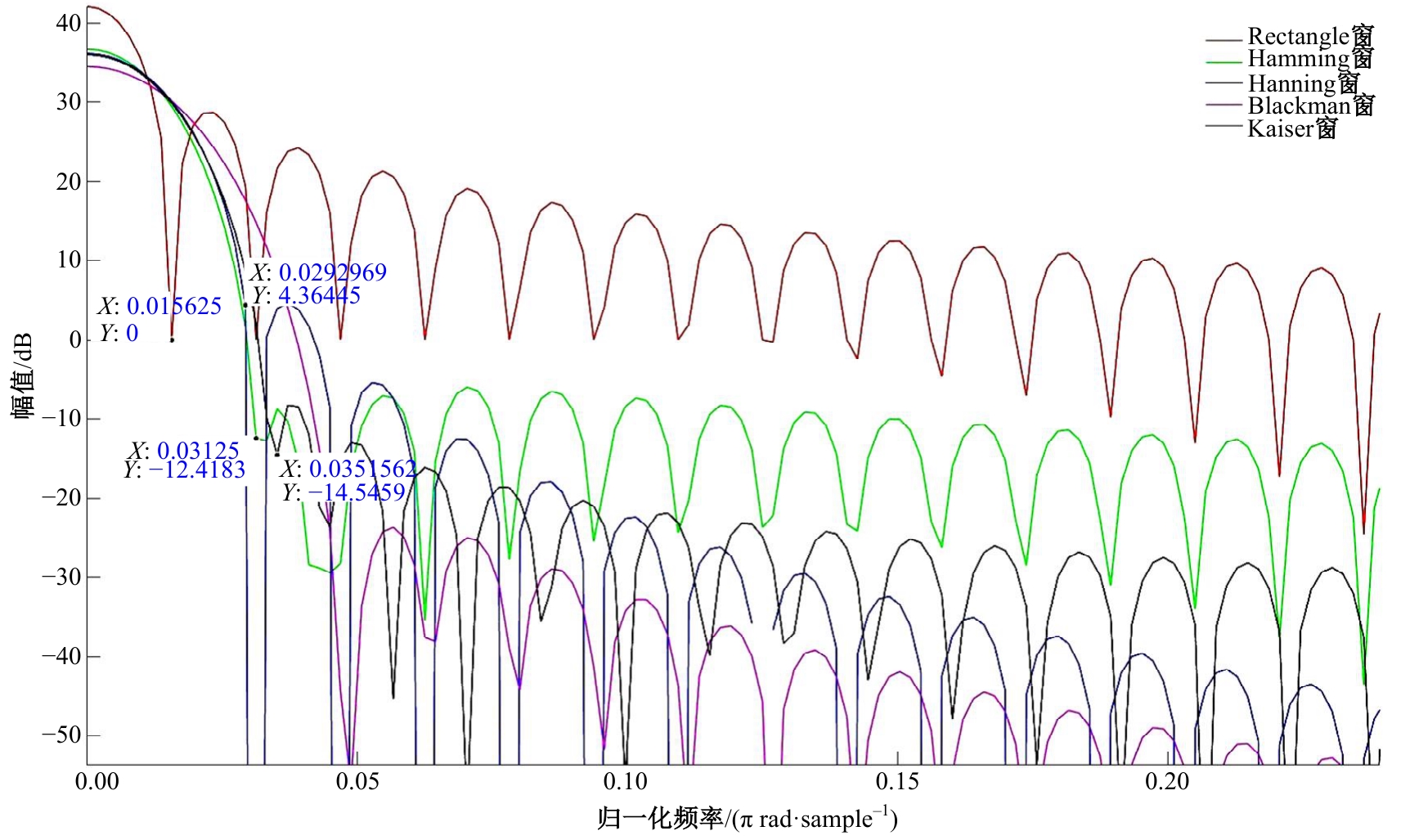

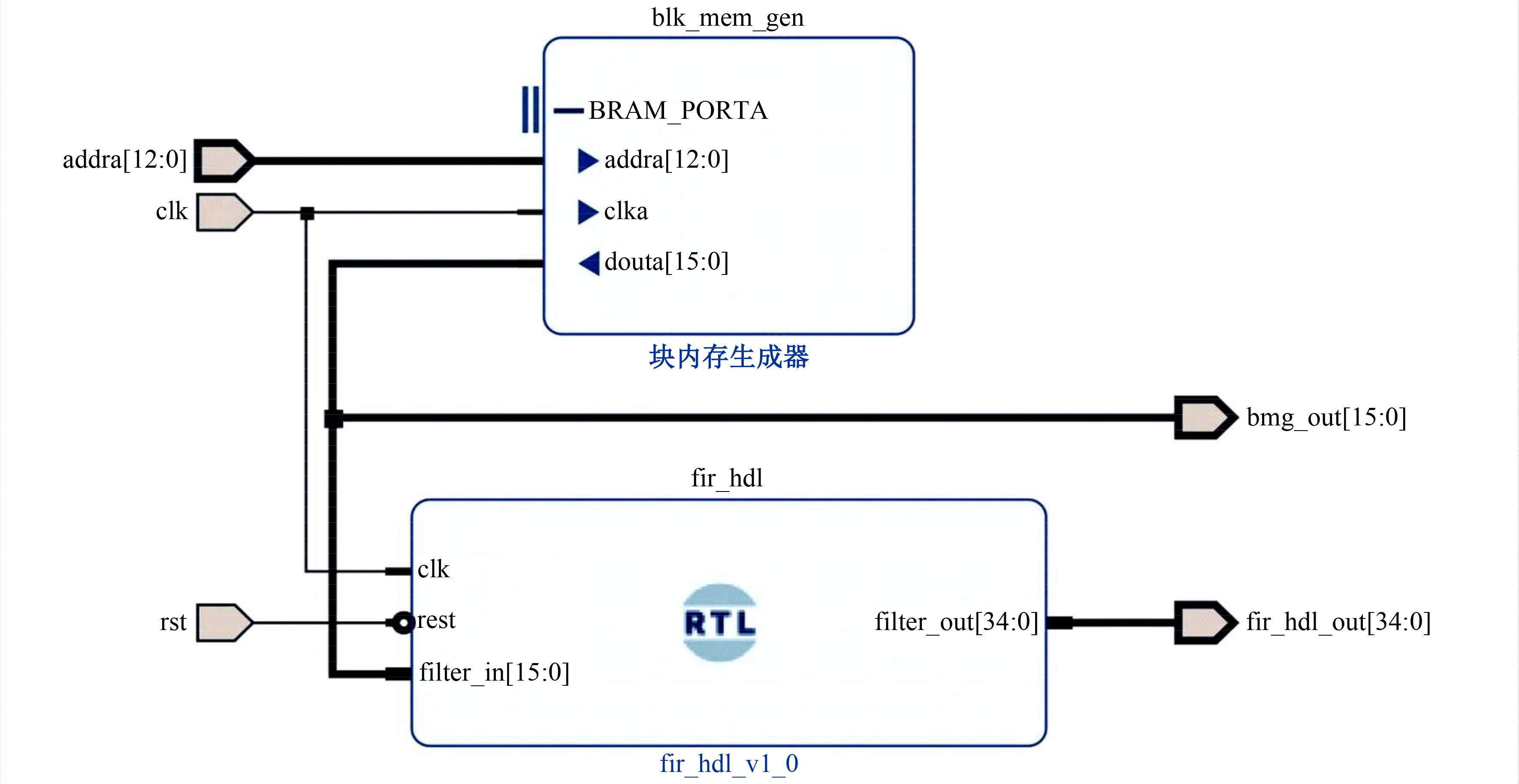

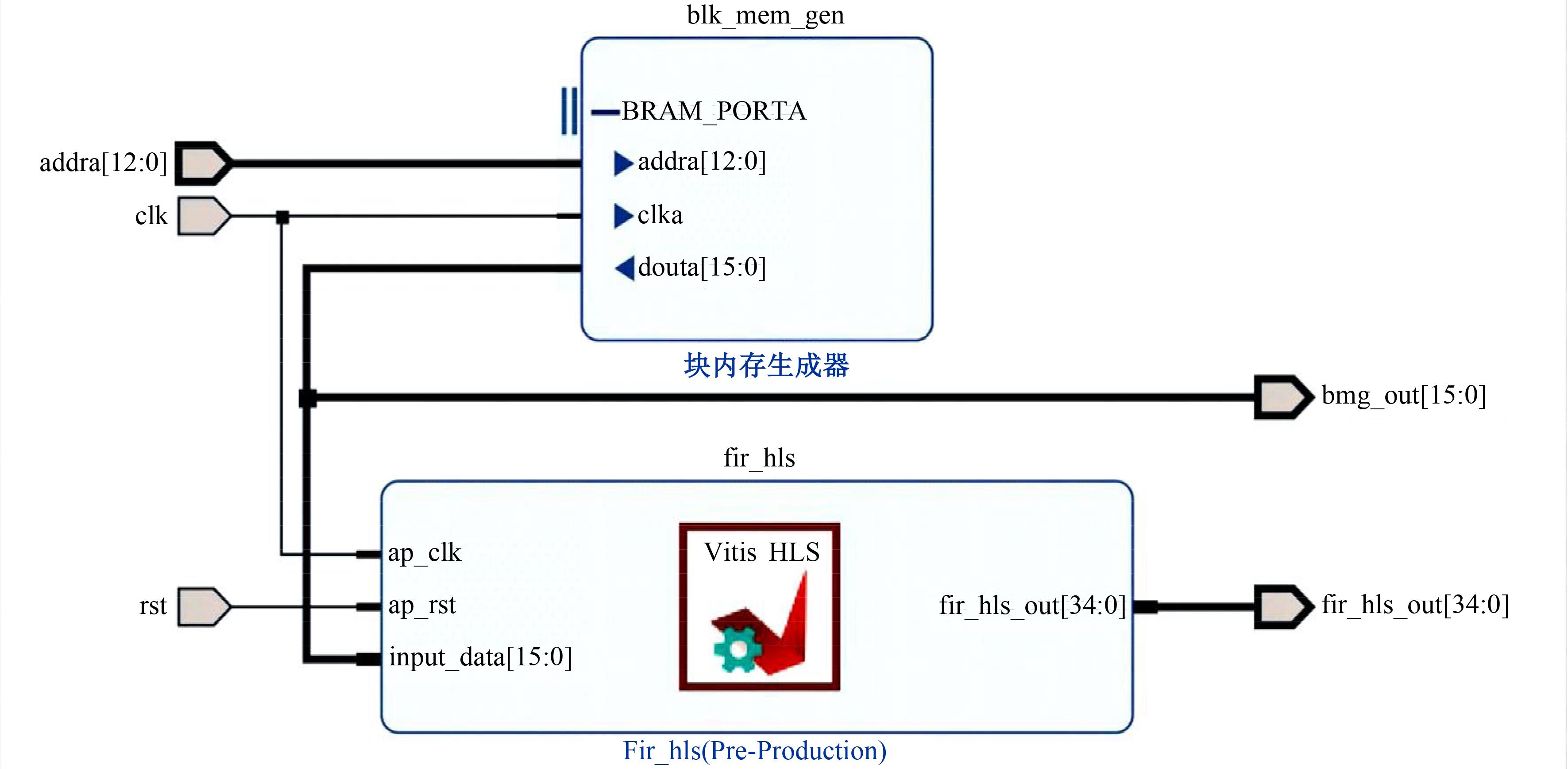

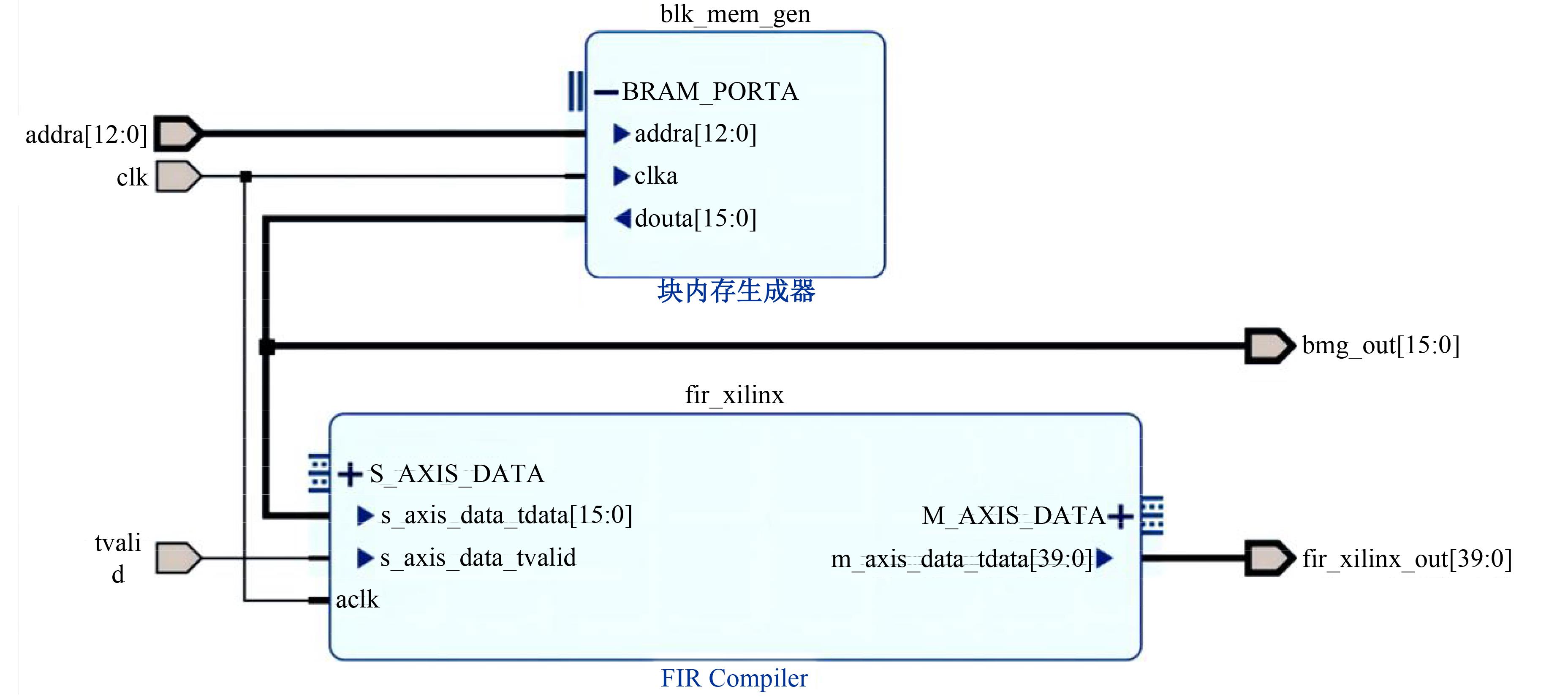

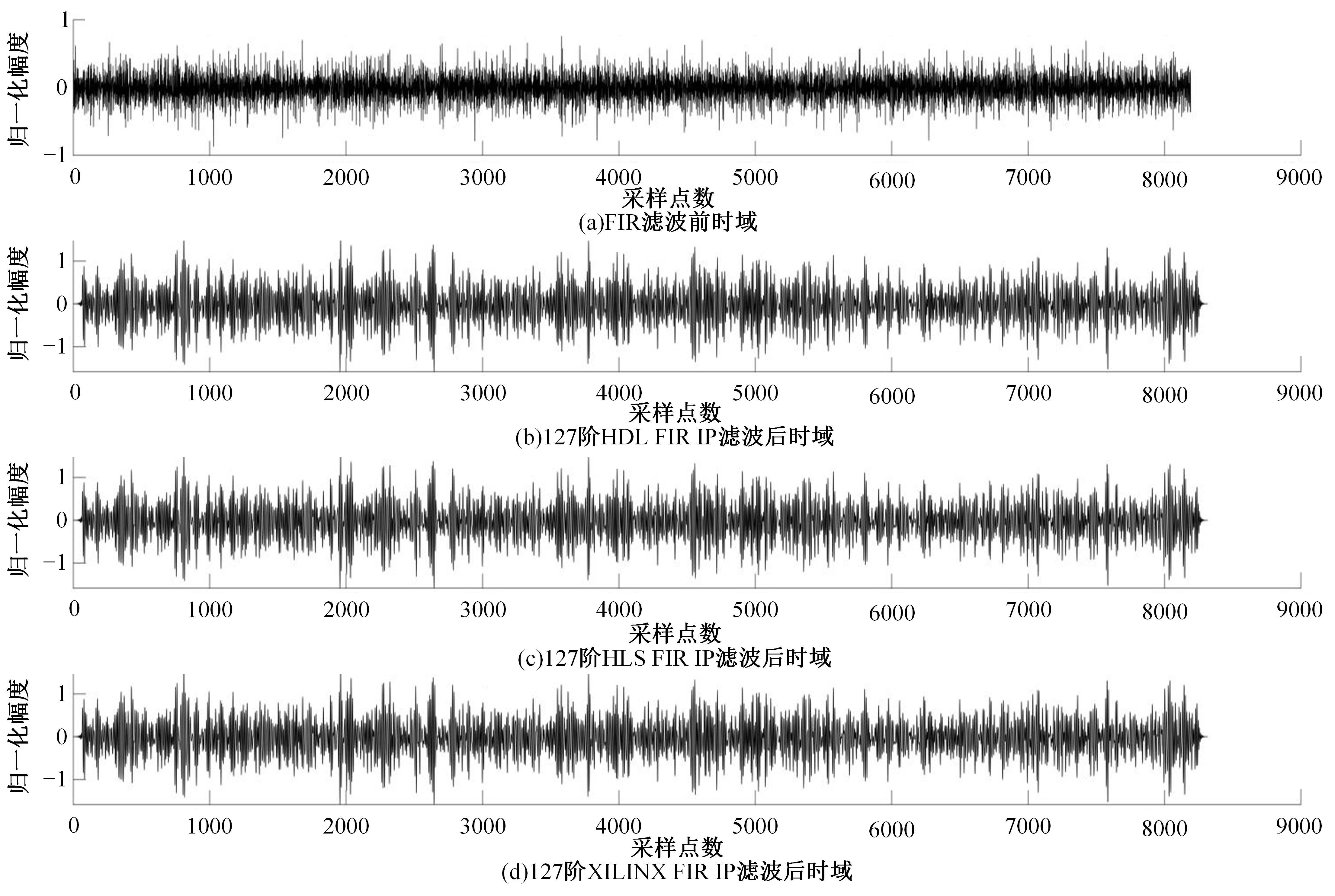

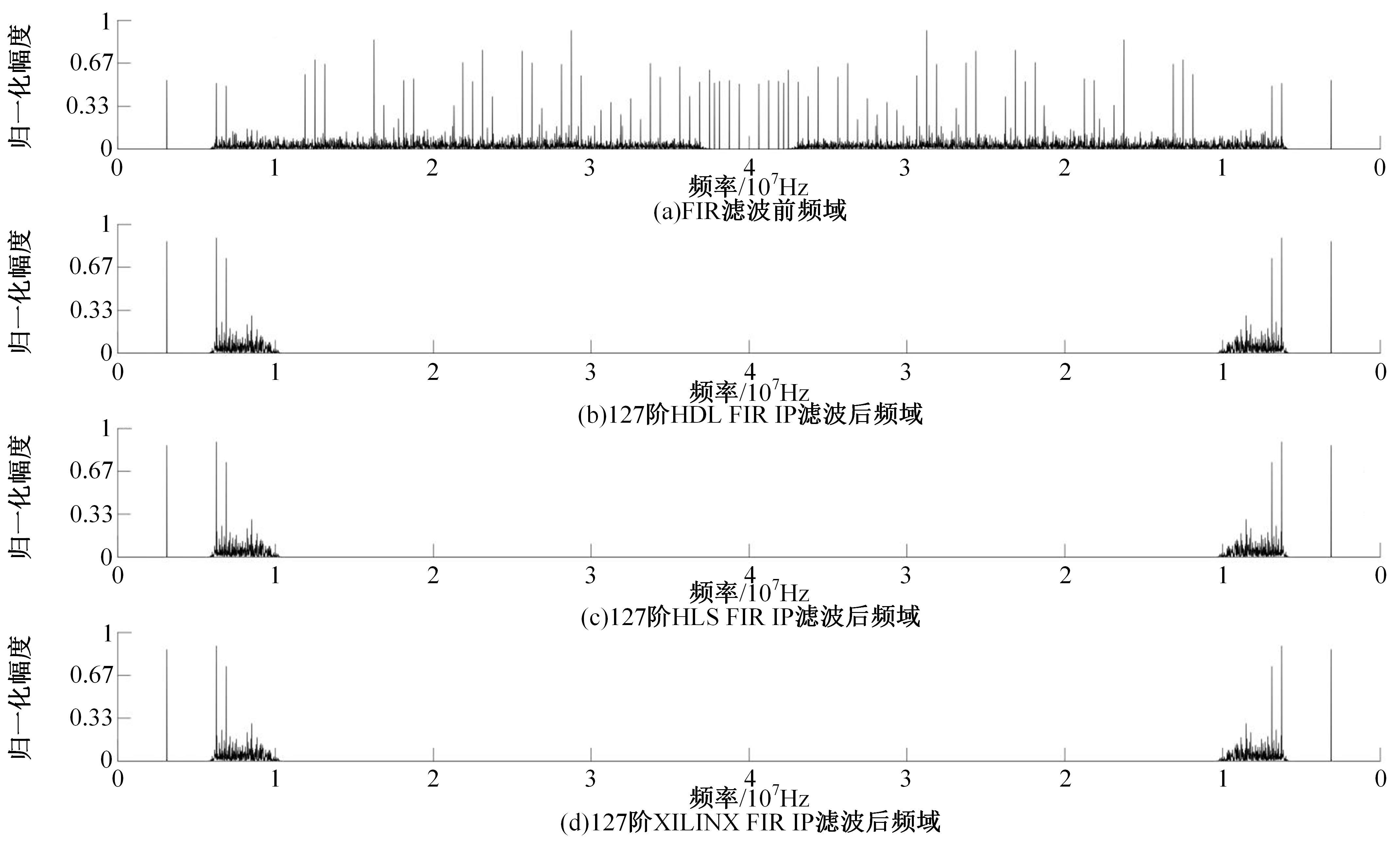

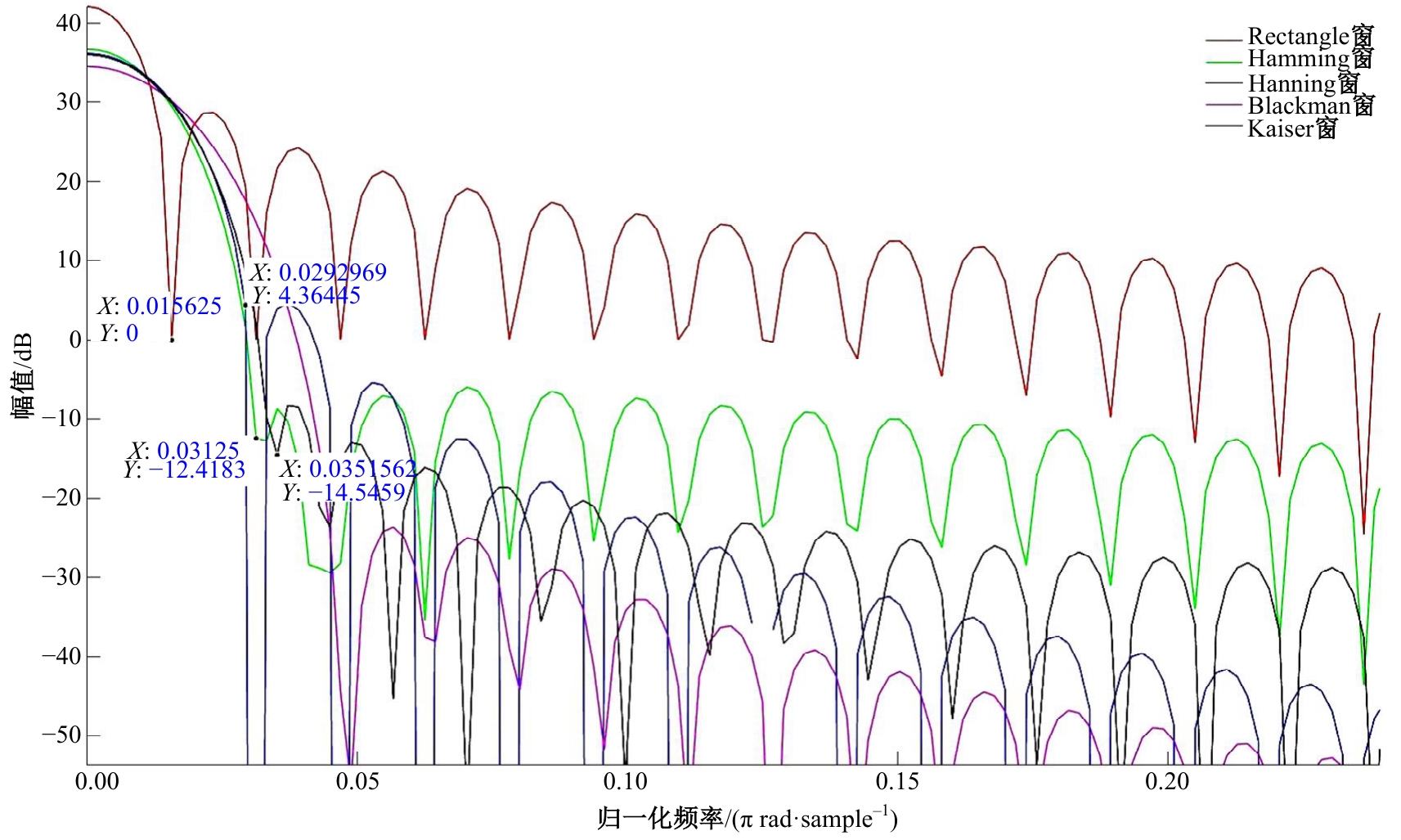

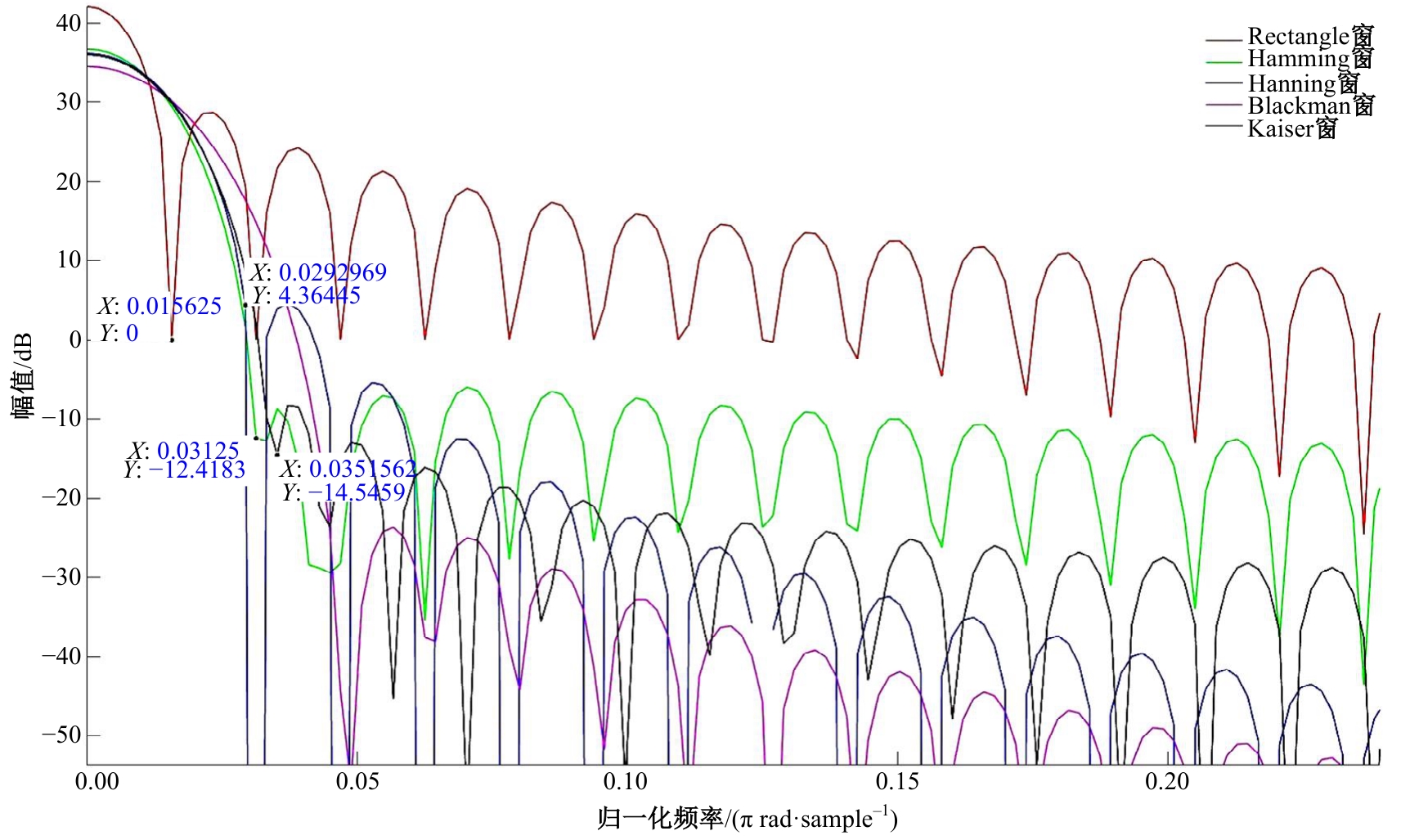

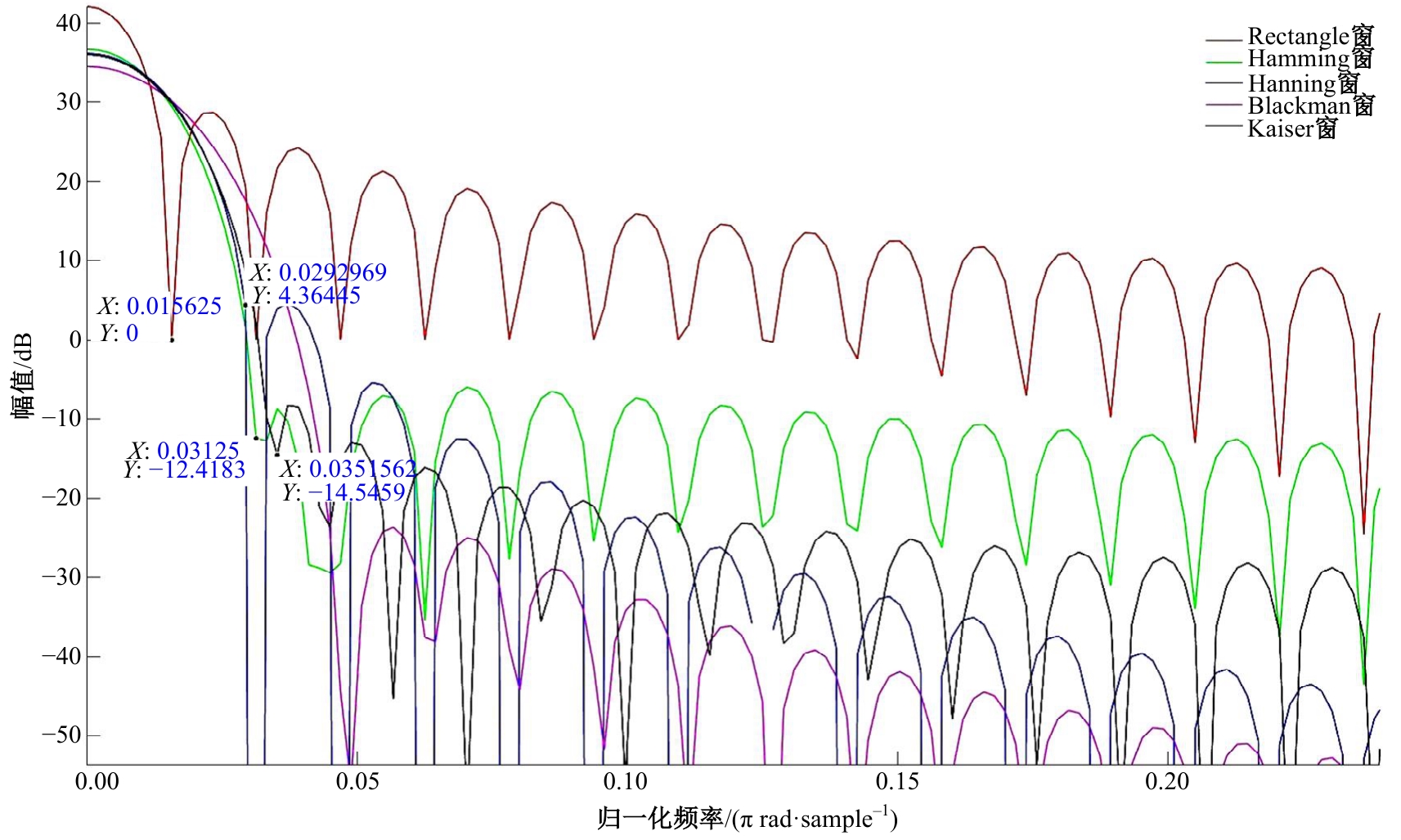

针对硬件开发过程中存在编程效率低、开发难度高及Vivado HLS资源使用率高等问题,利用Vivado及Vitis HLS平台设计并实现了基于127阶Hamming窗的流水线式直接型并行结构有限冲激响应滤波器,在Vivado Simulator环境下对比了HDL FIR IP、HLS FIR IP与XILINX FIR IP的滤波表现,详细分析了不同实现方式在资源使用率、时序、功耗、执行时间等方面的差异。实验结果表明:在相同条件下HLS FIR IP相较HDL FIR IP及XILINX FIR IP的资源使用率降低了1%,执行时间分别降低了24.5%、808.2%,且代码量节省了98.5%。以本文实验方法为基础与前人工作进行对比,客观分析了在一定条件下不同开发平台及方式的效率差异,结果表明本文设计方法可显著降低逻辑单元和存储资源的使用率,并提升开发效率。

中图分类号:

- TP301.6

| 1 | 周柚, 杨森, 李大琳, 等. 基于现场可编程门电路的人脸检测识别加速平台[J]. 吉林大学学报: 工学版,2019, 49(6): 2051-2057. |

| Zhou You, Yang Sen, Li Da-lin, et al. Acceleration platform for face detection and recognition based on field programmable gate array[J]. Journal of Jilin University (Engineering and Technology Edition), 2019, 49(6): 2051-2057. | |

| 2 | 汤嘉武, 郑龙, 廖小飞, 等.面向高性能图计算的高效高层次综合方法[J]. 计算机研究与发展, 2021, 58(3): 467-478. |

| Tang Jia-wu, Zheng Long, Liao Xiao-fei, et al. Effective high-level synthesis for high-performance graph processing[J]. Journal of Computer Research and Development, 2021, 58(3): 467-478. | |

| 3 | Schledt D, Kebschull U, Blume C. Developing a cluster-finding algorithm with Vitis HLS for the CBM-TRD[J]. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers[J].Detectors and Associated Equipment, 2023, 1047: No.167797. |

| 4 | Inc Xilinx. Versal ACAP hardware, IP, and platform development methodology guide (UG 1387) [EB/OL].[2022-11-16].. |

| 5 | Inc Xilinx. Vivado design suite user guide: designing with IP (UG 896) [EB/OL]. [2022-11-02]. |

| 6 | Lan H, Li D L, Wang K P, et al. A survey on performance optimization of high-level synthesis tools[J]. Journal of Computer Science and Technology, 2020, 35: 697-720. |

| 7 | Millón R, Frati E, Rucci E. A comparative study between HLS and HDL on SoC for image processing applications[J/OL].[2023-05-16]. |

| 8 | Srilakshmi S, Madhumati G L. A comparative analysis of HDL and HLS for developing CNN accelerators[C]∥Third International Conference on Artificial Intelligence and Smart Energy (ICAIS), Coimbatore, India, 2023: 1060-1065. |

| 9 | 张海龙, 张萌, 张亚州, 等. 基于临界采样多相滤波器组的宽带信号信道化器设计与实现[J]. 吉林大学学报: 工学版, 2023, 53(8): 2388-2394. |

| Zhang Hai-long, Zhang Meng, Zhang Ya-zhou, et al. Design and implementation of wideband signal channelizer based on critical sampling polyphase filter bank[J]. Journal of Jilin University (Engineering and Technology Edition),2023, 53(8): 2388-2394. | |

| 10 | Nosov E, Marshalov D, Fedotov L, et al. Multifunctional digital backend for quasar VLBI network[J]. Journal of Instrumentation, 2021, 16(5): No.P05003. |

| 11 | Smith J P, Bailey J I, Tuthill J, et al. A high-throughput oversampled polyphase filter bank using vivado hls and pynq on a rfsoc[J]. IEEE Open Journal of Circuits and Systems, 2021, 2: 241-252. |

| 12 | Hossain K, Ahmed R, Haque A, et al. A review of digital fir filter design in communication systems[J]. International Journal of Science and Research (IJSR), 2021, 10(2): 1380-1391. |

| 13 | Zwagerman M D. High level synthesis, a use case comparison with hardware description language[D].Michigan: Grand Valley State University, 2015. |

| 14 | Inc Xilinx.2022.1 release highlights[DB/OL].[2023-05-16] .. |

| 15 | Inc Xilinx. What's new for the vitis software platform[DB/OL].[2023-05-16] . |

| [1] | 张海龙,张萌,张亚州,王杰,冶鑫晨,王万琼,李嘉,杜旭,张婷. 基于临界采样多相滤波器组的宽带信号信道化[J]. 吉林大学学报(工学版), 2023, 53(8): 2388-2394. |

|

||