Journal of Jilin University(Engineering and Technology Edition) ›› 2024, Vol. 54 ›› Issue (6): 1746-1755.doi: 10.13229/j.cnki.jdxbgxb.20230042

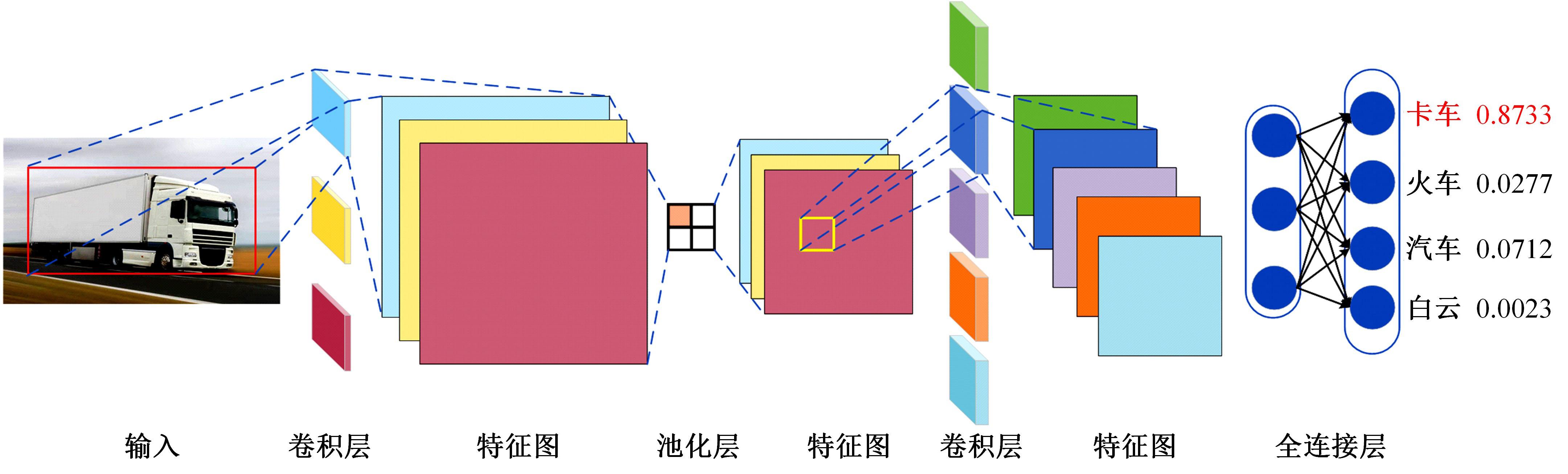

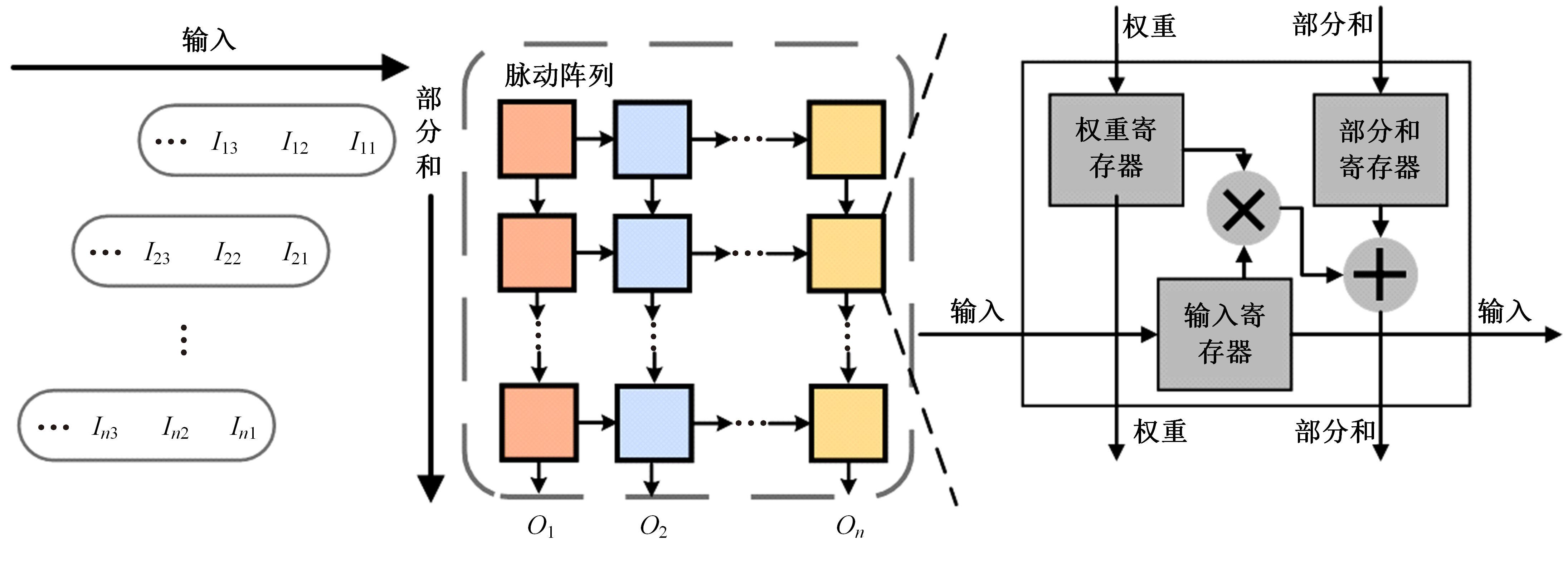

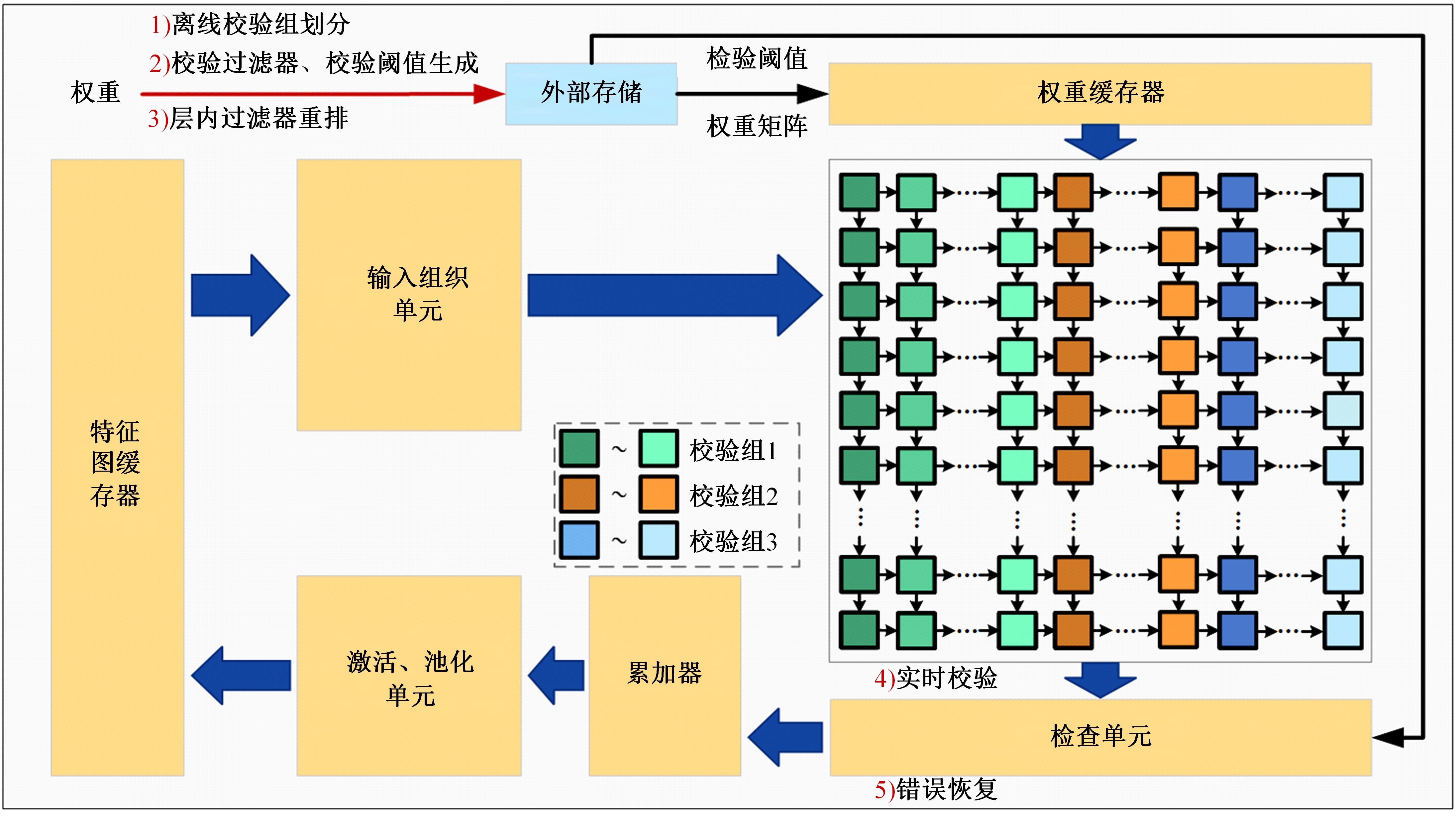

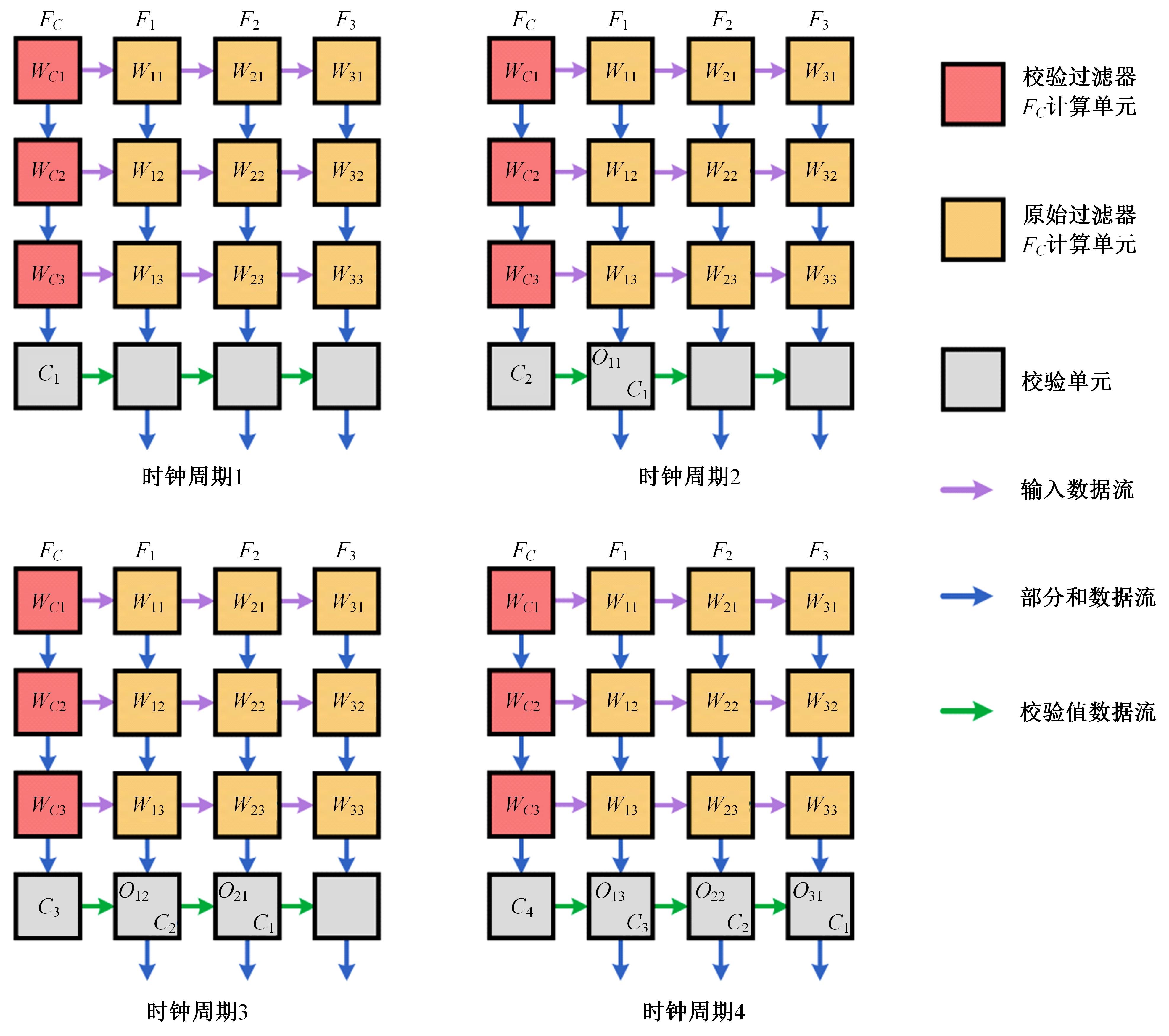

Systolic array-based CNN accelerator soft error approximate fault tolerance design

Xiao-hui WEI( ),Chen-yang WANG,Qi WU,Xin-yang ZHENG,Hong-mei YU(

),Chen-yang WANG,Qi WU,Xin-yang ZHENG,Hong-mei YU( ),Heng-shan YUE

),Heng-shan YUE

- College of Computer Science & Technology,Jilin University,Changchun 130012,China

CLC Number:

- TP302.8

| 1 | Peccerillo B, Mannino M, Mondelli A, et al. A survey on hardware accelerators: taxonomy, trends, challenges, and perspectives[J]. Journal of Systems Architecture, 2022, 129: No.102561. |

| 2 | 秦华标, 曹钦平. 基于FPGA的卷积神经网络硬件加速器设计[J]. 电子与信息学报, 2019, 41(11):2599-2605. |

| Qin Hua-biao, Cao Qin-ping. Design of convolutional neural networks hardware acceleration based on FPGA[J]. Ournal of Electronics & Information Technology, 2019, 41(11): 2599-2605. | |

| 3 | Chen Y H, Emer J, Sze V. Eyeriss: a spatial architecture for energy-efficient dataflow for convolutional neural networks[J]. ACM SIGARCH Computer Architecture News, 2016, 44(3): 367-379. |

| 4 | Du Z, Fasthuber R, Chen T, et al. ShiDianNao: shifting vision processing closer to the sensor[C]∥Proceedings of the 42nd Annual International Symposium on Computer Architecture,Portland,USA, 2015: 92-104. |

| 5 | Jouppi N P, Young C, Patil N, et al. In-datacenter performance analysis of a tensor processing unit[C]∥Proceedings of the 44th Annual International Symposium on Computer Architecture, Los Angeles,USA, 2017: 1-12. |

| 6 | Mittal S. A survey on modeling and improving reliability of DNN algorithms and accelerators[J]. Journal of Systems Architecture, 2020, 104: No.101689. |

| 7 | Azizimazreah A, Gu Y, Gu X, et al. Tolerating soft errors in deep learning accelerators with reliable on-chip memory designs[C]∥2018 IEEE International Conference on Networking, Architecture and Storage (NAS), Chongqing, China, 2018: 1-10. |

| 8 | Choi W, Shin D, Park J, et al. Sensitivity based error resilient techniques for energy efficient deep neural network accelerators[C]∥Proceedings of the 56th Annual Design Automation Conference, Las Vegas, USA, 2019: 1-6. |

| 9 | Tan J, Li Z, Fu X. Soft-error reliability and power co-optimization for GPGPUS register file using resistive memory[C]∥2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2015: 369-374. |

| 10 | Schorn C, Guntoro A, Ascheid G. Accurate neuron resilience prediction for a flexible reliability management in neural network accelerators[C]∥2018 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 2018: 979-984. |

| 11 | Sánchez A, Entrena L, Kastensmidt F. Approximate TMR for selective error mitigation in FPGAs based on testability analysis[C]∥2018 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Dresden, Germany, 2018: 112-119. |

| 12 | 周飞燕, 金林鹏, 董军. 卷积神经网络研究综述[J]. 计算机学报, 2017, 40(6): 1229-1251. |

| Zhou Fei-yan. Jin Lin-peng, Dong Jun. Review of convolutional neural network[J]. Chinese Journal of Computers, 2017, 40(6): 1229-1251. | |

| 13 | Samajdar A, Joseph J M, Zhu Y H, et al. A systematic methodology for characterizing scalability of dnn accelerators using scale-sim[C]∥2020 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), Virtual, Boston, USA, 2020: 58-68. |

| 14 | Hoang L H, Hanif M A, Shafique M. Ft-clipact: resilience analysis of deep neural networks and improving their fault tolerance using clipped activation[C]∥2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France,2020: 1241-1246. |

| 15 | 林景栋, 吴欣怡, 柴毅, 等. 卷积神经网络结构优化综述[J]. 自动化学报, 2020, 46(1): 24-37. |

| Lin Jing-dong, Wu Xin-yi, Chai Yi,et al. Structure optimization of convolutional neural networks: a survey[J]. Acta Automatica Sinica, 2020, 46(1): 24-37. | |

| 16 | Kahatapitiya K, Rodrigo R. Exploiting the redundancy in convolutional filters for parameter reduction[C]∥Proceedings of the IEEE/CVF Winter Conference on Applications of Computer Vision, Virtual, Hawaii, USA, 2021: 1410-1420. |

| 17 | Denil M, Shakibi B, Dinh L, et al. Predicting parameters in deep learning[EB/OL]. [2022-12-08]. |

| [1] | Chao XIA,Meng-jia WANG,Jian-yue Zhu,Zhi-gang YANG. Reduced-order modelling of a bluff body turbulent wake flow field using hierarchical convolutional neural network autoencoder [J]. Journal of Jilin University(Engineering and Technology Edition), 2024, 54(4): 874-882. |

| [2] | Guo-jun YANG,Ya-hui QI,Xiu-ming SHI. Review of bridge crack detection based on digital image technology [J]. Journal of Jilin University(Engineering and Technology Edition), 2024, 54(2): 313-332. |

| [3] | Xiang-jiu CHE,Huan XU,Ming-yang PAN,Quan-le LIU. Two-stage learning algorithm for biomedical named entity recognition [J]. Journal of Jilin University(Engineering and Technology Edition), 2023, 53(8): 2380-2387. |

| [4] | Zhen-hai ZHANG,Kun JI,Jian-wu DANG. Crack identification method for bridge based on BCEM model [J]. Journal of Jilin University(Engineering and Technology Edition), 2023, 53(5): 1418-1426. |

| [5] | Pei-yong LIU,Jie DONG,Luo-feng XIE,Yang-yang ZHU,Guo-fu YIN. Surface defect detection algorithm of magnetic tiles based on multi⁃branch convolutional neural network [J]. Journal of Jilin University(Engineering and Technology Edition), 2023, 53(5): 1449-1457. |

| [6] | Feng-le ZHU,Yi LIU,Xin QIAO,Meng-zhu HE,Zeng-wei ZHENG,Lin SUN. Analysis of hyperspectral image based on multi-scale cascaded convolutional neural network [J]. Journal of Jilin University(Engineering and Technology Edition), 2023, 53(12): 3547-3557. |

| [7] | Hai-long GAO,Yi-bo XU,De-zao HOU,Xue-song WANG. Short⁃term traffic flow prediction algorithm for road network based on deep asynchronous residual network [J]. Journal of Jilin University(Engineering and Technology Edition), 2023, 53(12): 3458-3464. |

| [8] | Jun-jie WANG,Yuan-jun NONG,Li-te ZHANG,Pei-chen ZHAI. Visual relationship detection method based on construction scene [J]. Journal of Jilin University(Engineering and Technology Edition), 2023, 53(1): 226-233. |

| [9] | Xuan-jing SHEN,Xue-feng ZHANG,Yu WANG,Yu-bo JIN. Multi⁃focus image fusion algorithm based on pixel⁃level convolutional neural network [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(8): 1857-1864. |

| [10] | Ming-hua GAO,Can YANG. Traffic target detection method based on improved convolution neural network [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(6): 1353-1361. |

| [11] | Huai-jiang YANG,Er-shuai WANG,Yong-xin SUI,Feng YAN,Yue ZHOU. Simplified residual structure and fast deep residual networks [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(6): 1413-1421. |

| [12] | Xue-zhi WANG,Qing-liang LI,Wen-hui LI. Spatio⁃temporal model of soil moisture prediction integrated with transfer learning [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(3): 675-683. |

| [13] | Xiang-jun LI,Jie-ying TU,Zhi-bin ZHAO. Validity classification of melting curve based on multi⁃scale fusion convolutional neural network [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(3): 633-639. |

| [14] | Xian-tong LI,Wei QUAN,Hua WANG,Peng-cheng SUN,Peng-jin AN,Yong-xing MAN. Route travel time prediction on deep learning model through spatiotemporal features [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(3): 557-563. |

| [15] | Wen-zhi GAO,Yan-jun WANG,Xin-wei WANG,Pan ZHANG,Yong LI,Yang DONG. Real⁃time diagnosis for misfire fault of diesel engine based on convolutional neural network [J]. Journal of Jilin University(Engineering and Technology Edition), 2022, 52(2): 417-424. |

|

||